Product Specification

# NM9A02G08 NAND Flash Memory Datasheet 3.3V, x8 2G-BIT NAND Flash

Product Specification

### **Table of Contents**

| NM   | 9A02G08             | 3 NA   | ND Flash Memory Datasheet 3.3V, x8 2G-BIT NAND Flash      | 1  |

|------|---------------------|--------|-----------------------------------------------------------|----|

| Tab  | le of Con           | tents  | S                                                         | 2  |

| Figu | ures                |        |                                                           | 5  |

| Tab  | les                 |        |                                                           | 7  |

| 1.   | Feature             | s      |                                                           | 8  |

| 2.   | General Description |        |                                                           | 9  |

|      | 2.1.                | Pro    | duct List                                                 | 9  |

|      | 2.2.                | Pin    | Description                                               | 9  |

|      | 2.3.                | Bloo   | k Diagram                                                 | 10 |

|      | 2.4.                | Mei    | nory Organization                                         | 10 |

|      | 2.5.                | Arra   | y Addressing                                              | 11 |

|      | 2.6.                | Con    | nmand Set                                                 | 11 |

|      | 2.7.                | OTP    | Pages                                                     | 13 |

|      | 2.8.                | Lega   | acy OTP Commands                                          | 13 |

|      | 2.9.                | Dev    | ice Feature Table                                         | 13 |

|      | 2.9.                | 1.     | Feature Address 01h: Timing Mode                          | 14 |

|      | 2.9.                | 2.     | Feature Address 80h: Programmable I/O Drive Strength      | 14 |

|      | 2.9.                | 3.     | Feature Address 81h: Programmable R/B# Pull-Down Strength | 15 |

|      | 2.9.                | 4.     | Feature Address 90h: Array Operation Mode                 | 15 |

|      | 2.10.               | Dev    | ice ID                                                    | 15 |

|      | 2.10.1.             |        | ID: Address 00h                                           | 16 |

|      | 2.10                | ).2.   | ID: Address 20h (ONFI Signature)                          | 16 |

|      | 2.11.               | Para   | imeter Page                                               | 17 |

|      | 2.12.               | Unio   | que ID                                                    | 18 |

|      | 2.13.               | Stat   | us Register                                               | 19 |

|      | 2.14.               | Bloo   | k Lock Feature                                            | 19 |

|      | 2.14                | 1.1.   | WP# and Block Lock                                        | 20 |

|      | 2.14                | 1.2.   | Boundary Block Address Registers And Invert Area Bit      | 20 |

|      | 2.14                | 1.3.   | Block Lock Addressing                                     | 21 |

|      | 2.14                | 1.4.   | Block Lock Status Register                                | 21 |

|      | 2.14                | 1.5.   | Block Lock Flow                                           | 22 |

| 3.   | Bus Ope             | eratio | ons                                                       | 22 |

|      | 3.1.                | Asy    | nchronous Interface Mode Selection                        | 22 |

|      | 3.2.                | Star   | ndby                                                      | 23 |

|      | 3.3.                | Asy    | nchronous Command Input                                   | 23 |

|      | 3.4.                | Asy    | nchronous Address Input                                   | 23 |

|      | 3.5.                | Asy    | nchronous Data Input                                      | 24 |

|      | 3.6. Asy            |        | nchronous Data Output (Normal)                            | 24 |

|      | 3.7.                | Asy    | nchronous Data Output (EDO)                               | 25 |

|      | 3.8.                | Wri    | te Protect                                                | 25 |

|      | 3.9.                | Rea    | dy/Busy#                                                  | 26 |

| 4.   | Device (            | Oper   | ations                                                    | 26 |

| DS009 (v | DS009 (v1.0) Oct 28, 2020 Product Specification |                                               |    |  |  |

|----------|-------------------------------------------------|-----------------------------------------------|----|--|--|

| 4.1.     | Res                                             | et                                            |    |  |  |

|          | 4.1.1.                                          | Reset (FFh)                                   |    |  |  |

| 4.2.     | Rea                                             | d ID (90h)                                    |    |  |  |

| 4.3.     | Rea                                             | d Parameter Page (ECh)                        |    |  |  |

| 4.4.     | Rea                                             | d Unique ID (EDh)                             |    |  |  |

| 4.5.     | Fea                                             | ture Operations                               |    |  |  |

|          | 4.5.1.                                          | Get Features (EEh)                            |    |  |  |

|          | 4.5.2.                                          | Set Features (EFh)                            |    |  |  |

| 4.6.     | Stat                                            | us Operations                                 |    |  |  |

|          | 4.6.1.                                          | Read Status (70h)                             |    |  |  |

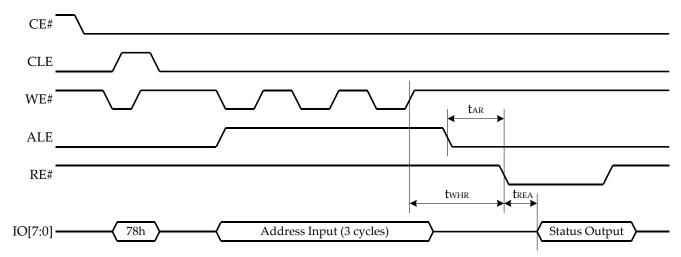

|          | 4.6.2.                                          | Read Status Enhanced (78h)                    |    |  |  |

| 4.7.     | Colu                                            | umn Address Operations                        |    |  |  |

|          | 4.7.1.                                          | Random Data Read (05h-E0h)                    |    |  |  |

|          | 4.7.2.                                          | Random Data Read Two-Plane (06h-E0h)          |    |  |  |

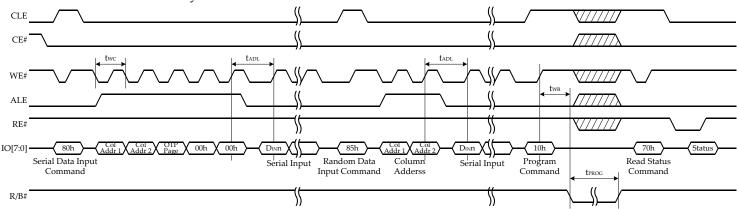

|          | 4.7.3.                                          | Random Data Input (85h)                       |    |  |  |

|          | 4.7.4.                                          | Program For Internal Data Input (85h)         |    |  |  |

| 4.8.     | Rea                                             | d Operations                                  |    |  |  |

|          | 4.8.1.                                          | Read Mode (00h)                               |    |  |  |

|          | 4.8.2.                                          | Read Page (00h-30h)                           |    |  |  |

|          | 4.8.3.                                          | Read Page Cache Sequential (31h)              |    |  |  |

|          | 4.8.4.                                          | Read Page Cache Random (00h-31h)              |    |  |  |

|          | 4.8.5.                                          | Read Page Cache Last (3Fh)                    |    |  |  |

| 4.9.     | Pro                                             | gram Operations                               |    |  |  |

|          | 4.9.1.                                          | Program Page (80h-10h)                        |    |  |  |

|          | 4.9.2.                                          | Program Page Cache (80h-15h)                  |    |  |  |

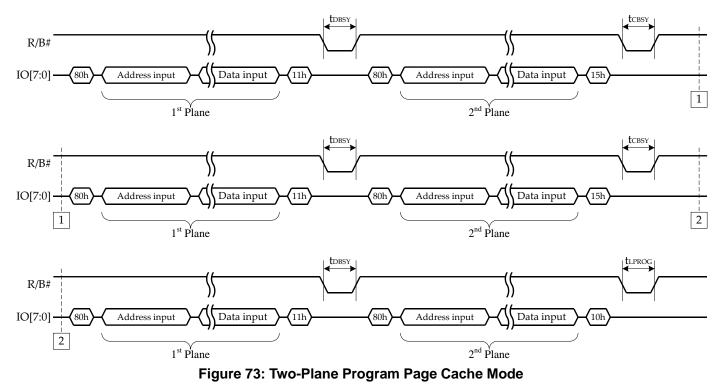

|          | 4.9.3.                                          | Program Page Two-Plane (80h-11h)              |    |  |  |

| 4.10     | ). Eras                                         | e Operations                                  |    |  |  |

|          | 4.10.1.                                         | Erase Block (60h-D0h)                         |    |  |  |

|          | 4.10.2.                                         | Erase Block Two-Plane (60h-D1h) Operation     |    |  |  |

| 4.11     | L. Inte                                         | rnal Data Move Operations                     |    |  |  |

|          | 4.11.1.                                         | Read For Internal Data Move (00h-35h)         |    |  |  |

|          | 4.11.2.                                         | Program For Internal Data Move (85h-10h)      |    |  |  |

|          | 4.11.3.                                         | ECC Concerns in Internal Data Move Operations |    |  |  |

| 4.12     | 2. Bloo                                         | k Lock Feature                                |    |  |  |

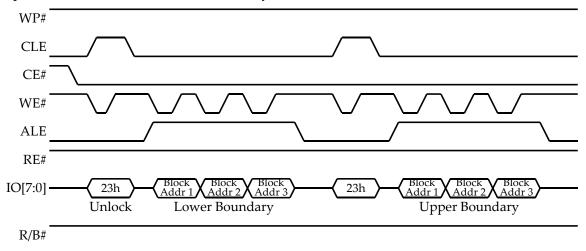

|          | 4.12.1.                                         | Unlock (23h, 24h)                             |    |  |  |

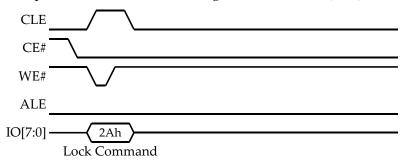

|          | 4.12.2.                                         | Lock (2Ah)                                    |    |  |  |

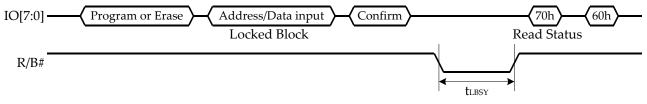

|          | 4.12                                            | 2.2.1. Effect On Program Or Erase Operations  |    |  |  |

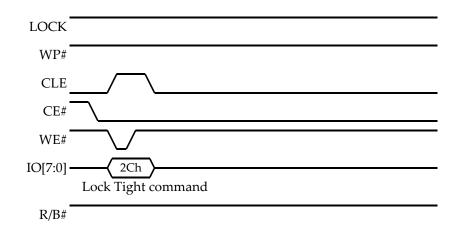

|          | 4.12.3.                                         | Lock Tight (2Ch)                              |    |  |  |

|          | 4.12                                            | 2.3.1. Effect On Program And Erase Operations |    |  |  |

|          | 4.12                                            | 2.3.2. Disabling Lock Tight                   |    |  |  |

|          | 4.12.4.                                         | Block Lock Read Status (7Ah)                  |    |  |  |

| 4.13     | 8. One                                          | P-Time Programmable (OTP) Operations          |    |  |  |

|          | 4.13.1.                                         | Legacy OTP Commands                           | 50 |  |  |

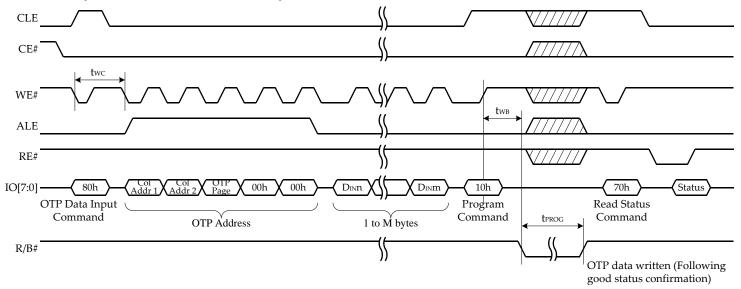

|          | 4.13.2.                                         | OTP Data Program (80h-10h)                    | 50 |  |  |

| Product | Specification |

|---------|---------------|

|---------|---------------|

| DS0 | DS009 (v1.0) Oct 28, 2020 Product Specification |                                                            |  |    |  |

|-----|-------------------------------------------------|------------------------------------------------------------|--|----|--|

|     | 4.13.3.                                         | Random Data Input (85h)                                    |  | 51 |  |

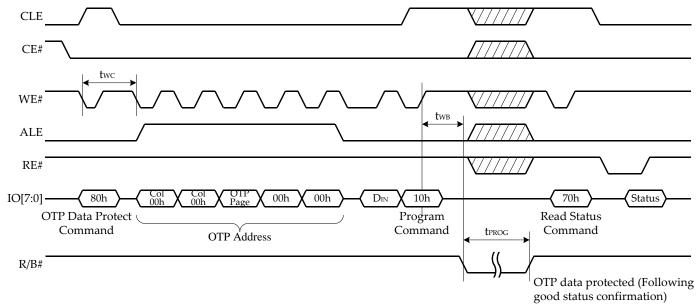

|     | 4.13.4.                                         | OTP Data Protect                                           |  | 51 |  |

|     | 4.13.5.                                         | OTP Page Read (00h-30h)                                    |  | 52 |  |

| 5.  | Two-Plane                                       | Operations                                                 |  | 53 |  |

|     | 5.1. Tw                                         | o-Plane Addressing                                         |  | 53 |  |

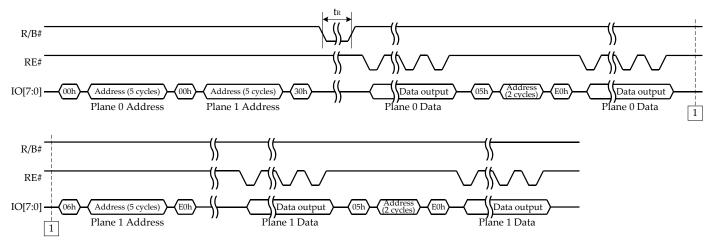

|     | 5.2. Tw                                         | vo-Plane Page Read                                         |  | 53 |  |

|     | 5.3. Tw                                         | vo-Plane Page Read with Random Data Read                   |  | 54 |  |

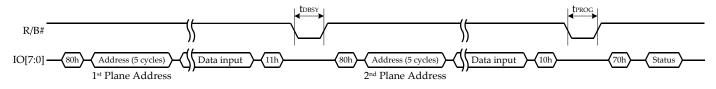

|     | 5.4. Tw                                         | o-Plane Program Page                                       |  | 54 |  |

|     | 5.5. Tw                                         | o-Plane Program Page with Random Data Input                |  | 54 |  |

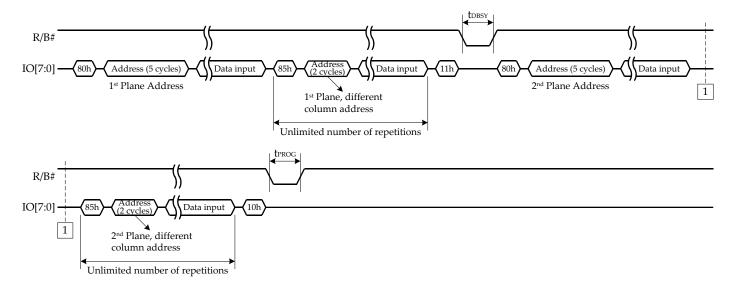

|     | 5.6. Tw                                         | vo-Plane Program Page Cache Mode                           |  | 55 |  |

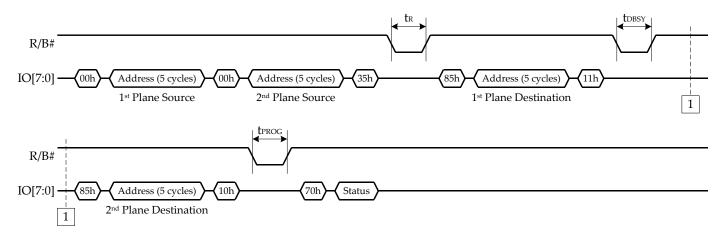

|     | 5.7. Tw                                         | o-Plane Internal Data Move                                 |  | 55 |  |

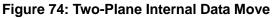

|     | 5.8. Tw                                         | o-Plane Internal Data Move with Two-Plane Random Data Read |  | 56 |  |

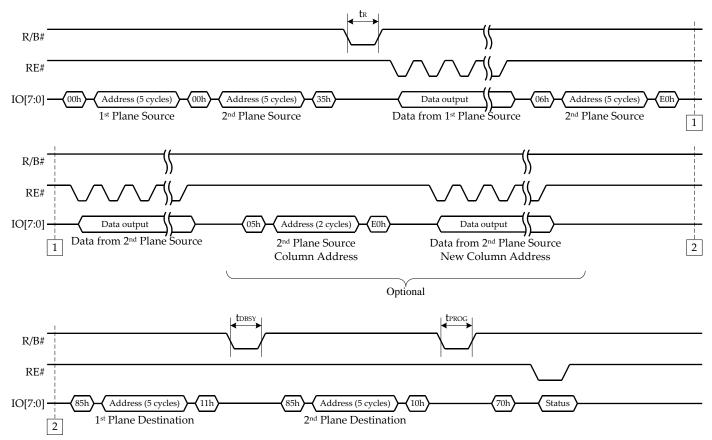

|     | 5.9. Tw                                         | o-Plane Internal Data Move with Random Data Input          |  | 56 |  |

|     | 5.10. Tw                                        | o-Plane Block Erase                                        |  | 57 |  |

|     | 5.11. Tw                                        | vo-Plane/Multiple-Die Read Status Cycle                    |  | 57 |  |

| 6.  | Interleaved                                     | Die (Multi-LUN) Operations                                 |  | 57 |  |

|     | 6.1. Int                                        | erleaved Die (Multi-LUN) Operation Completion              |  | 57 |  |

|     | 6.2. Ca                                         | che Operations in Interleaved Die (Multi-LUN) Operations   |  | 57 |  |

|     | 6.3. Pr                                         | ogram and Read in Interleaved Die (Multi-LUN) Operations   |  | 58 |  |

| 7.  | Error Mana                                      | gement                                                     |  | 58 |  |

|     | 7.1. Ba                                         | d Block                                                    |  | 58 |  |

|     | 7.2. Fa                                         | ctory Bad Blocks                                           |  | 58 |  |

|     | 7.3. Ba                                         | d Block Management                                         |  | 58 |  |

| 8.  | Internal EC                                     | C and Spare Area Mapping for ECC                           |  | 59 |  |

| 9.  | Electrical S                                    | pecifications                                              |  | 59 |  |

|     | 9.1. DO                                         | Characters and Operating Conditions                        |  | 60 |  |

|     | 9.2. AC                                         | Characteristics                                            |  | 62 |  |

|     | 9.2.1.                                          | Command, Data and Address Input                            |  | 62 |  |

|     | 9.2.2.                                          | Normal Operation                                           |  | 63 |  |

|     | 9.3. Pr                                         | ogram/Erase Characteristics                                |  | 64 |  |

| 10. | Part N                                          | umbering                                                   |  | 66 |  |

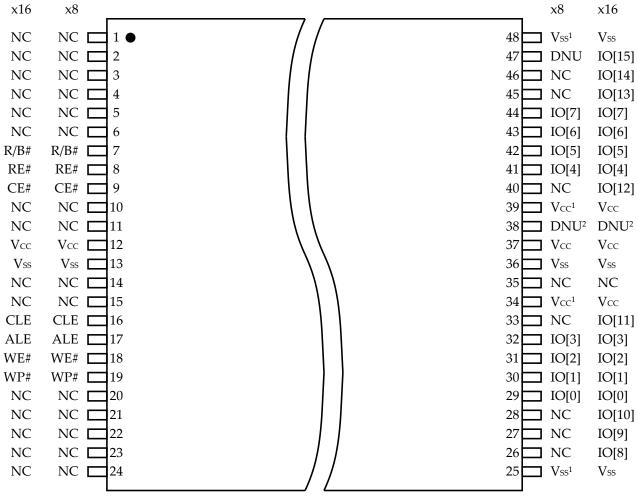

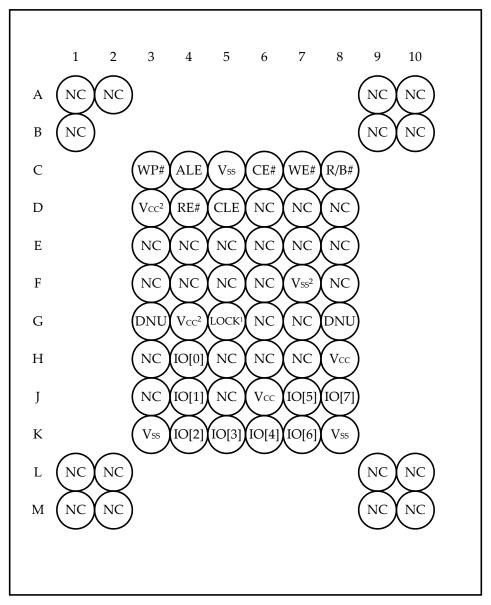

| 11. | Packa                                           | ge Information                                             |  | 66 |  |

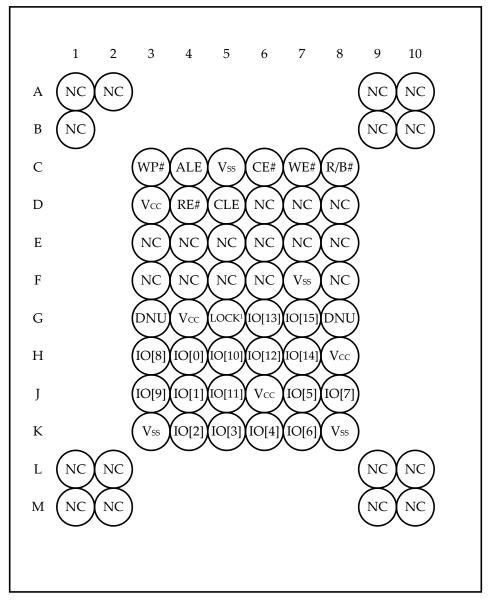

|     | 11.1. Sig                                       | nal Assignments                                            |  | 67 |  |

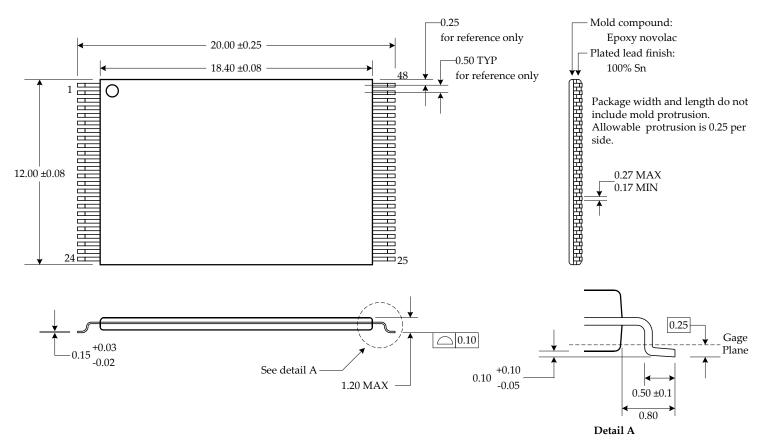

|     | 11.1.1.                                         | 48-Pin TSOP                                                |  | 67 |  |

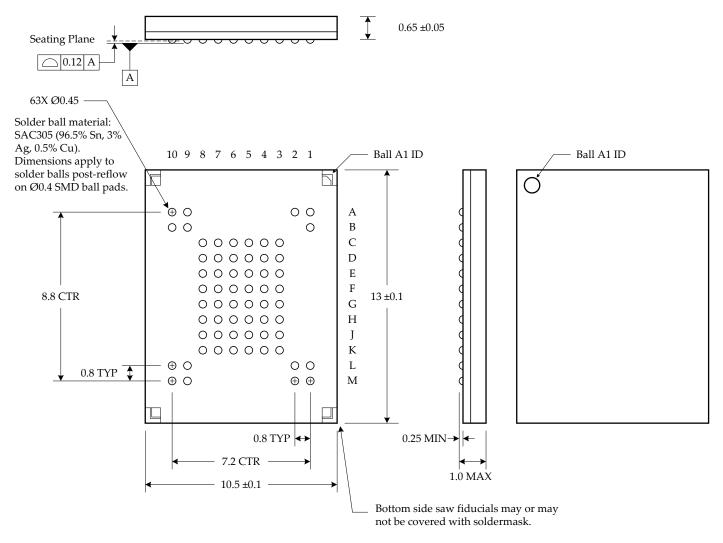

|     | 11.1.2.                                         | 63-Ball VFBGA, x8                                          |  | 68 |  |

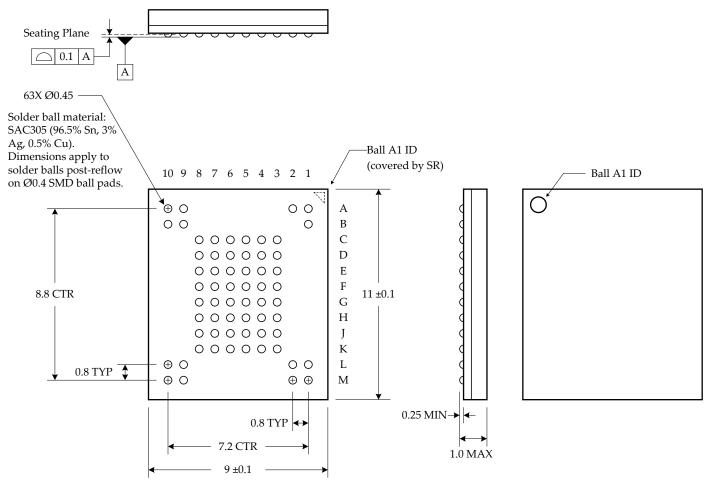

|     | 11.1.3.                                         | 63-Ball VFBGA, x16                                         |  | 69 |  |

|     | 11.2. Pa                                        | ckage Dimensions                                           |  | 70 |  |

|     | 11.2.1.                                         | 48-Pin TSOP                                                |  | 70 |  |

|     | 11.2.2.                                         | 63-Ball VFBGA (10.5mm x 13mm)                              |  | 71 |  |

|     | 11.2.3.                                         | 63-Ball VFBGA (9mm x 11mm)                                 |  | 72 |  |

| 12. | Revisio                                         | on History                                                 |  | 72 |  |

| 13. | . Important Notice                              |                                                            |  |    |  |

**Product Specification**

### **Figures**

| Figure 1: Logic Diagram                                            |    |

|--------------------------------------------------------------------|----|

| Figure 2: NAND Flash Block Diagram                                 |    |

| Figure 3: Array Organization                                       | 11 |

| Figure 4: Flash Array Protected: Invert Area Bit = 0               | 20 |

| Figure 5: Flash Array Protected: Invert Area Bit = 1               | 21 |

| Figure 6: Block Lock Flowchart                                     | 22 |

| Figure 7: Asynchronous Command Input Cycle Timing Diagram          | 23 |

| Figure 8: Asynchronous Address Input Cycle Timing Diagram          |    |

| Figure 9: Asynchronous Data Input Cycle Timing Diagram             |    |

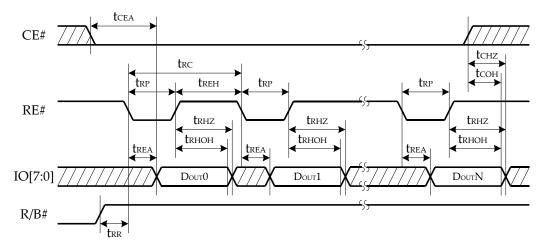

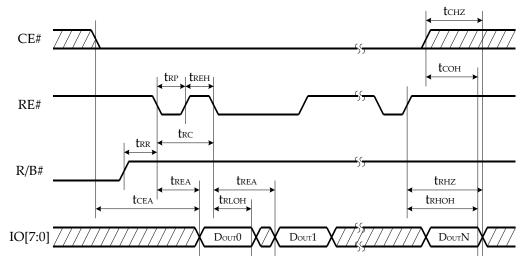

| Figure 10: Asynchronous Data Output Cycle (Normal) Timing Diagram  | 25 |

| Figure 11: Asynchronous Data Output Cycle (EDO) Timing Diagram     | 25 |

| Figure 12: R/B# Open-Drain Output                                  |    |

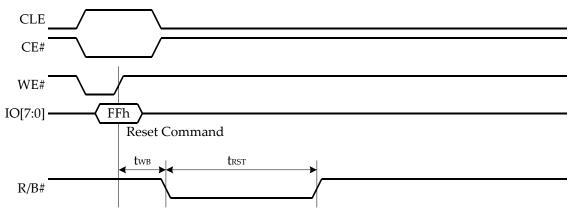

| Figure 13: Reset (FFh) Timing Diagram                              | 27 |

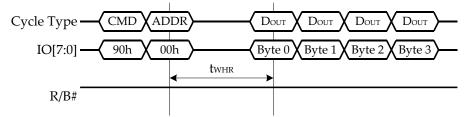

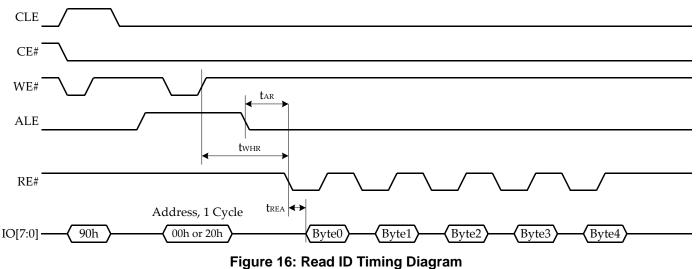

| Figure 14: Read ID Operation: Manufacture ID                       | 27 |

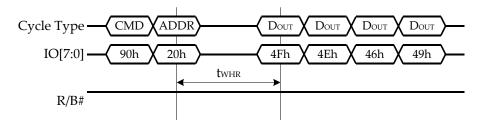

| Figure 15: Read ID Operation: ONFI Signature                       | 27 |

| Figure 16: Read ID Timing Diagram                                  | 27 |

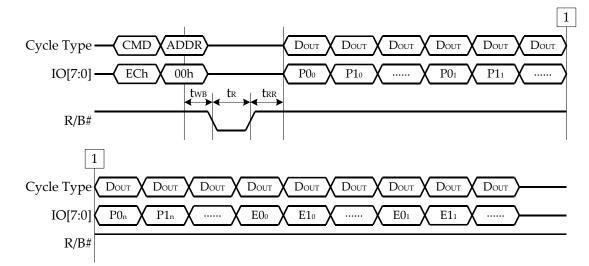

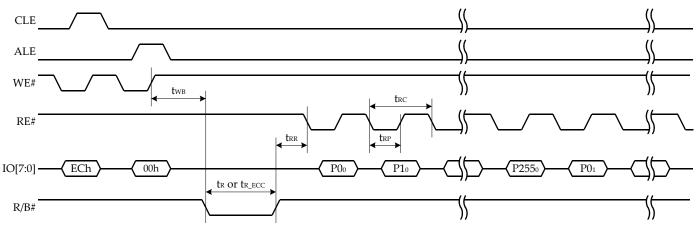

| Figure 17: Read Parameter Page Operation                           |    |

| Figure 18 Read Parameter Page Timing Diagram                       |    |

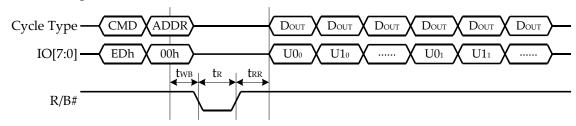

| Figure 19: Read Unique ID Operation                                |    |

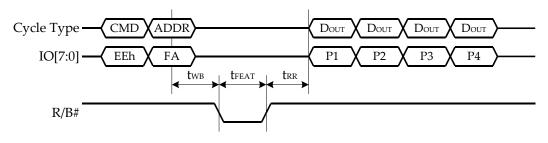

| Figure 20: Get Feature Operation                                   |    |

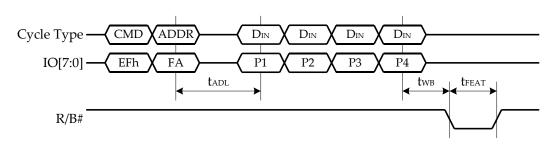

| Figure 21: Set Features Operation                                  |    |

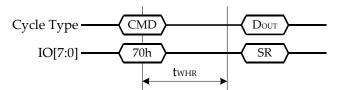

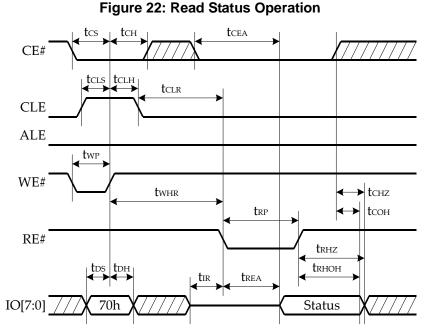

| Figure 22: Read Status Operation                                   |    |

| Figure 23: Read Status Timing Diagram                              |    |

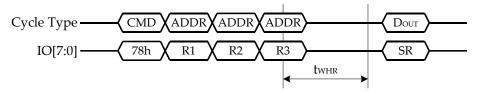

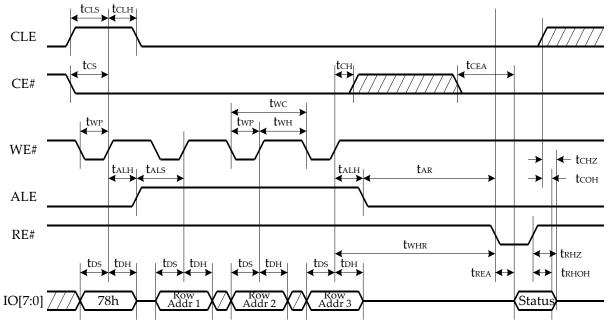

| Figure 24: Read Status Enhanced Operation                          |    |

| Figure 25: Read Status Enhanced Timing Diagram                     |    |

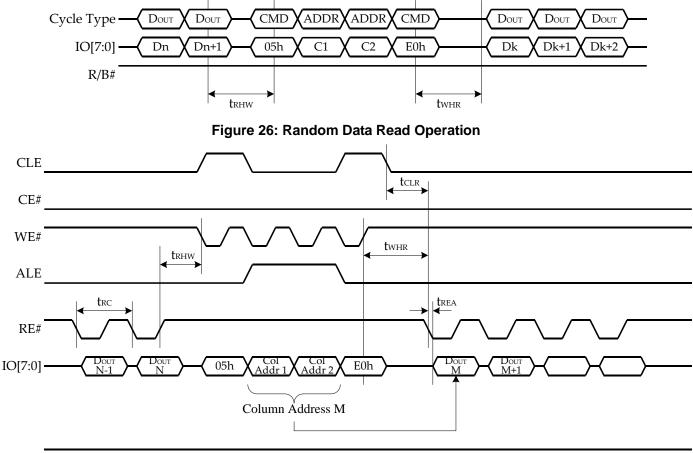

| Figure 26: Random Data Read Operation                              |    |

| Figure 27 Random Data Read Timing Diagram                          | 32 |

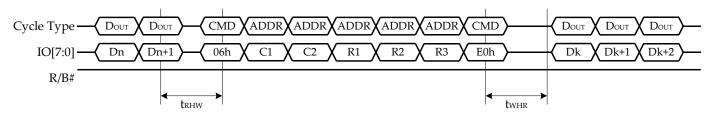

| Figure 28: Random Data Read Two-Plane Operation                    | 33 |

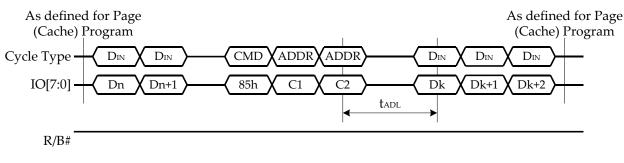

| Figure 29: Random Data Input Operation                             | 33 |

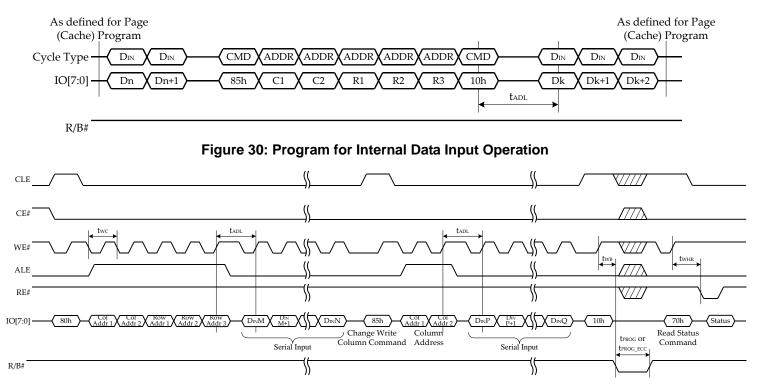

| Figure 30: Program for Internal Data Input Operation               |    |

| Figure 31: Program Page with Random Data Input Timing Diiagram     |    |

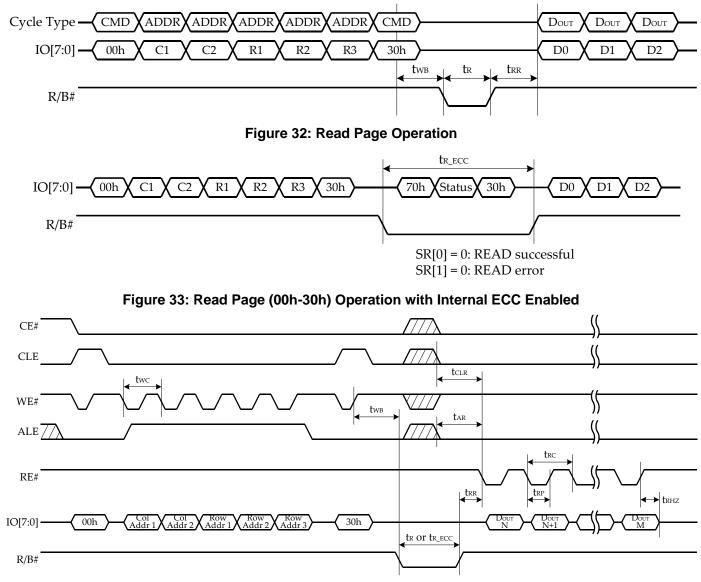

| Figure 32: Read Page Operation                                     | 35 |

| Figure 33: Read Page (00h-30h) Operation with Internal ECC Enabled | 35 |

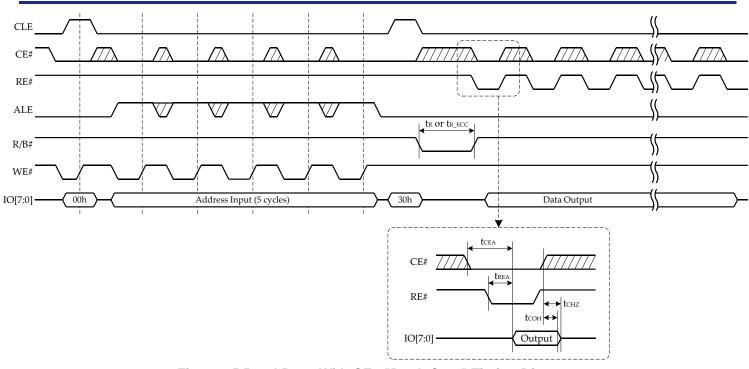

| Figure 34 Read Page Timing Diagram                                 |    |

| Figure 35 Read Page With CE# "Don't Care" Timing Diagram           |    |

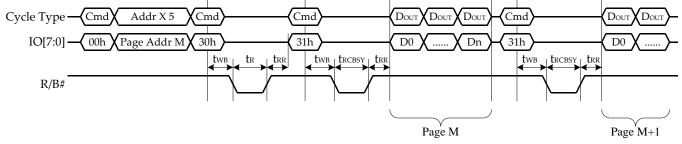

| Figure 36: Read Page Cache Sequential Operation                    |    |

| Figure 37 Read Page Cache Sequential Timing Diagram                |    |

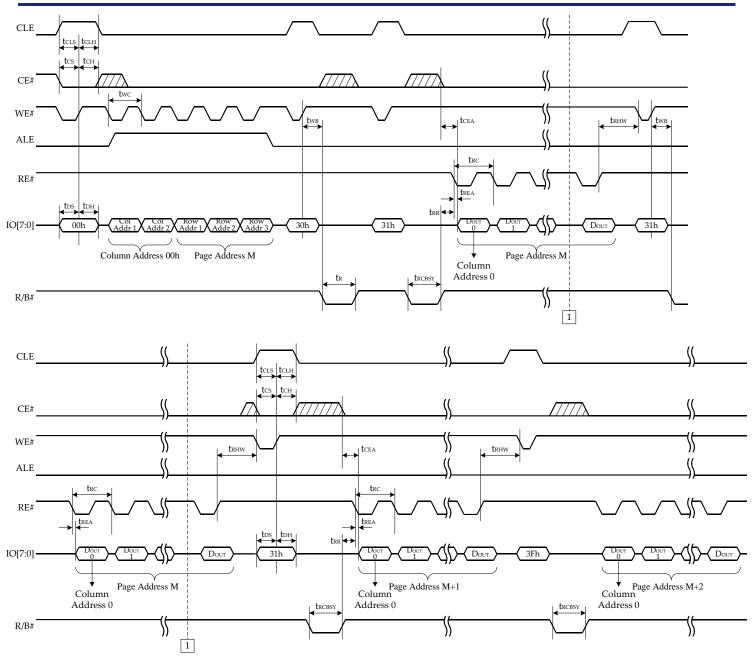

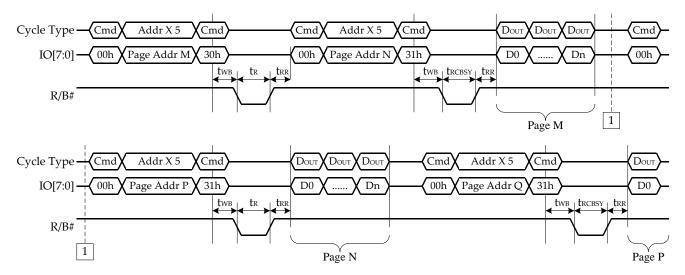

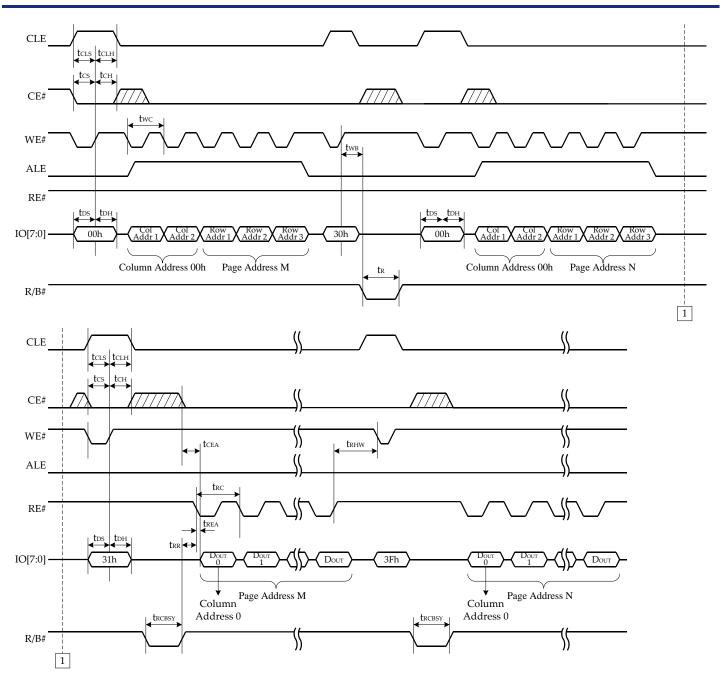

| Figure 38: Read Page Cache Random Operation                        |    |

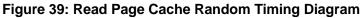

| Figure 39: Read Page Cache Random Timing Diagram                   |    |

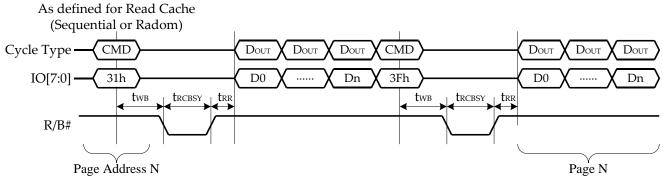

| Figure 40: Read Page Cache Last (3Fh) Operation                    | 40 |

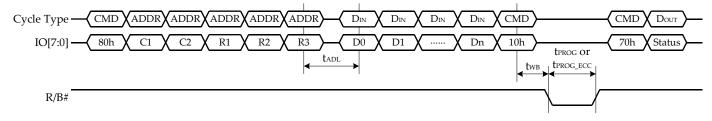

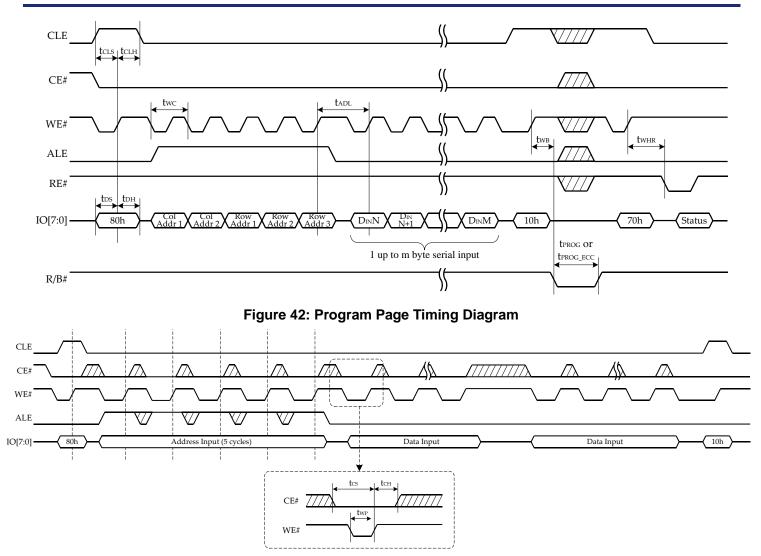

| Figure 41: Program Page Operation                                  | 40 |

| Figure 42: Program Page Timing Diagram                             |    |

**Product Specification**

|                                                                                              | Teatron |

|----------------------------------------------------------------------------------------------|---------|

| Figure 43: Program Page with CE# "Don't Care" Timing Diagram                                 | 41      |

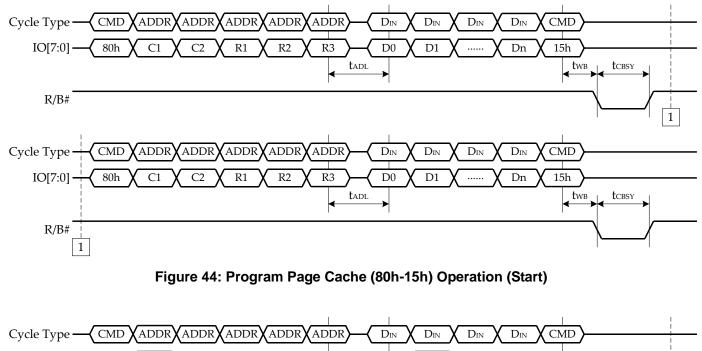

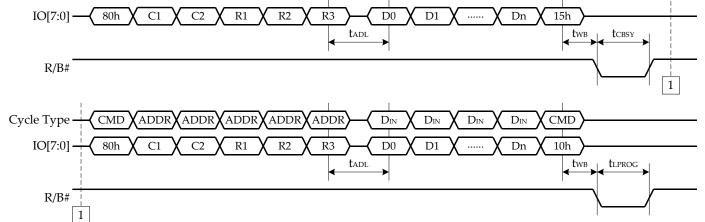

| Figure 44: Program Page Cache (80h-15h) Operation (Start)                                    | 42      |

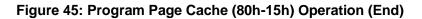

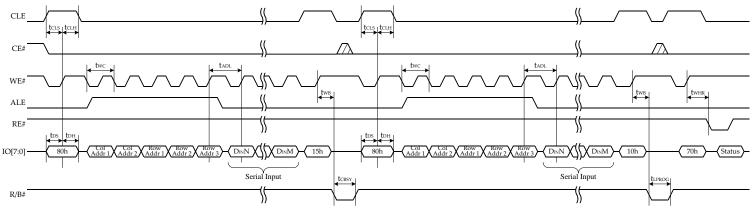

| Figure 45: Program Page Cache (80h-15h) Operation (End)                                      | 42      |

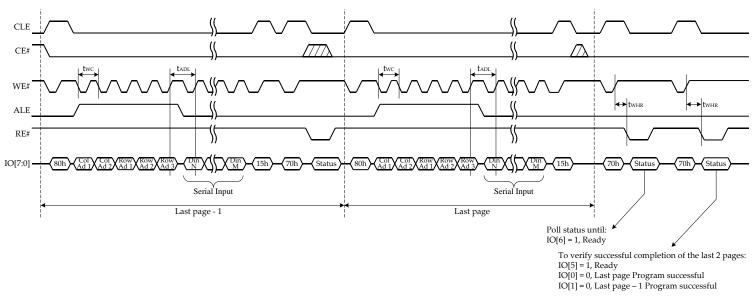

| Figure 46: Program Page Cache Timing Diagram                                                 | 42      |

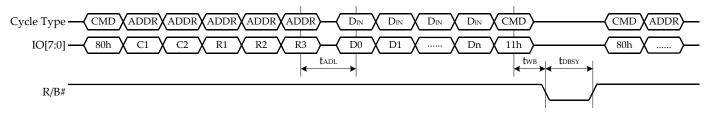

| Figure 47: Program Page Cache Ending on 15h                                                  | 43      |

| Figure 48: Program Page Two-Plane (80h-11h) Operation                                        | 43      |

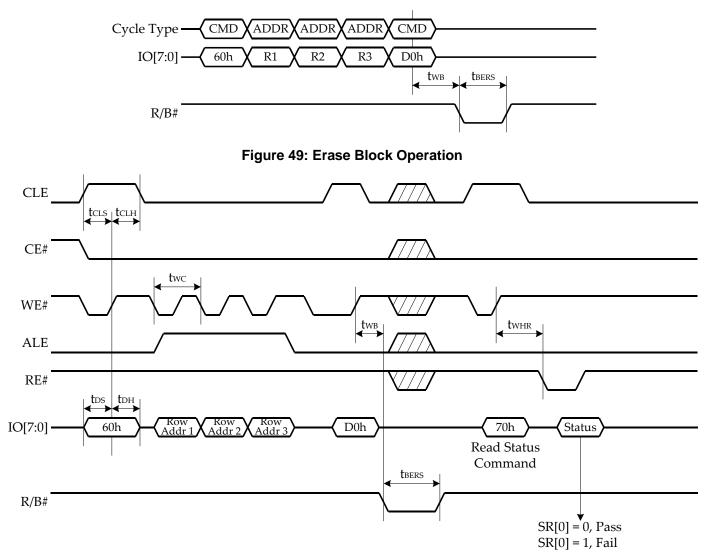

| Figure 49: Erase Block Operation                                                             | 44      |

| Figure 50: Erase Block Timing Diagram                                                        | 44      |

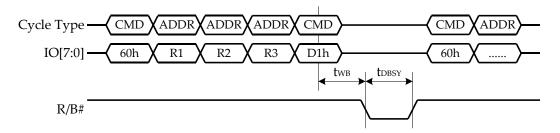

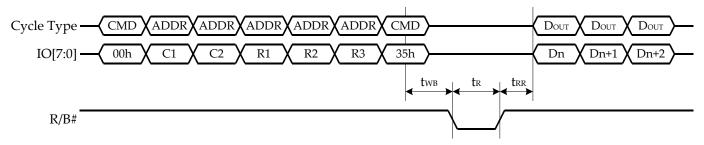

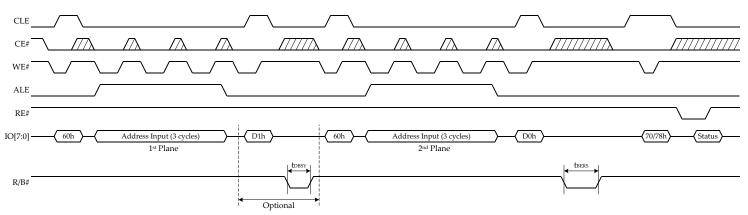

| Figure 51: Erase Block Two-Plane (60h-D1h) Operation                                         | 45      |

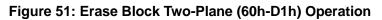

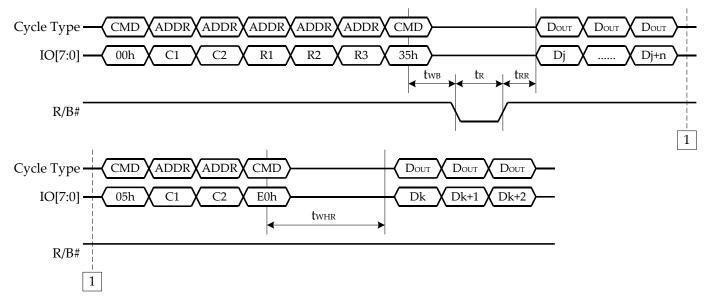

| Figure 52: Read For Internal Data Move (00h-35h) Operation                                   |         |

| Figure 53: Read For Internal Data Move (00h-35h) with Random Data Read (05h-E0h)             |         |

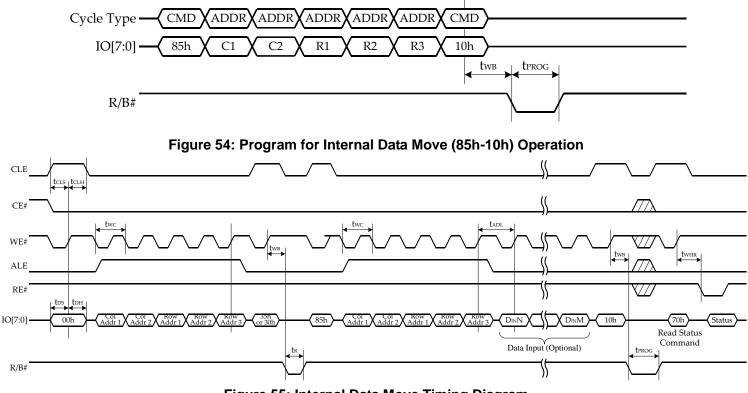

| Figure 54: Program for Internal Data Move (85h-10h) Operation                                |         |

| Figure 55: Internal Data Move Timing Diagram                                                 |         |

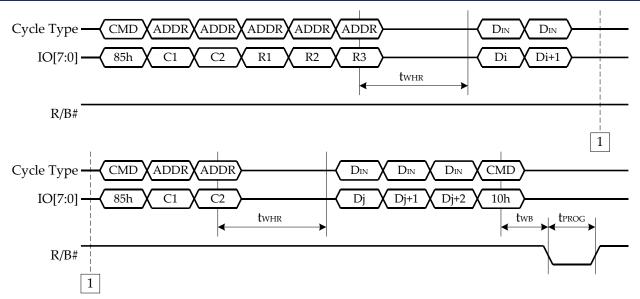

| Figure 56: Program for Internal Data Move (85h-10h) with Random Data Input (85h)             |         |

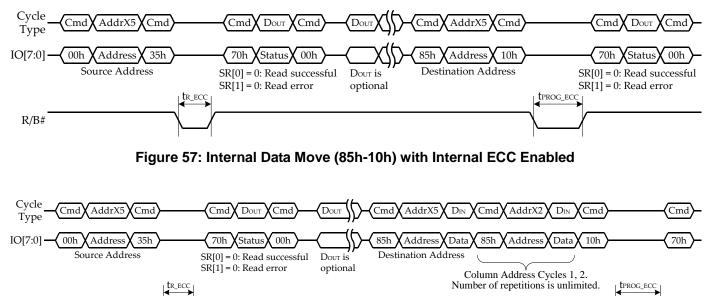

| Figure 57: Internal Data Move (85h-10h) with Internal ECC Enabled                            |         |

| Figure 58: Internal Data Move (85h-10h) with Random Data Input with Internal ECC Enabled     |         |

| Figure 59: Unlock Operations                                                                 |         |

| Figure 60: Lock Operation                                                                    |         |

| Figure 61: Program/Erase Command Issued to Locked Block                                      |         |

| Figure 62: Lock Tight Operation                                                              |         |

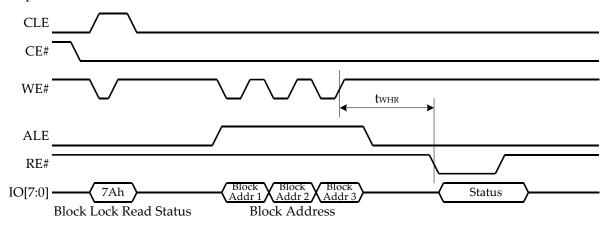

| Figure 63: Block Lock Read Status                                                            |         |

| Figure 64: OTP Data Program Operation (After Entering OTP Operation Mode)                    |         |

| Figure 65: OTP Data Program Operation with Random Data Input (After Entering OTP Operation   |         |

|                                                                                              |         |

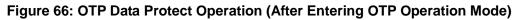

| Figure 66: OTP Data Protect Operation (After Entering OTP Operation Mode)                    |         |

| Figure 67: OTP Data Read Operation                                                           |         |

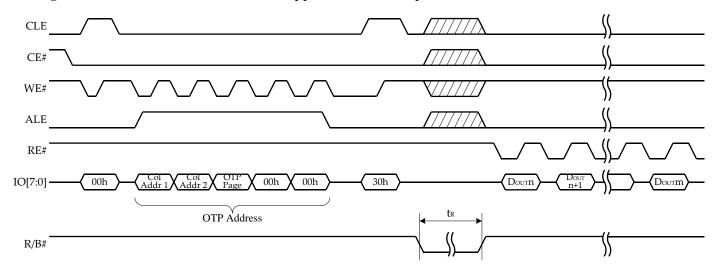

| Figure 68: OTP Data Read with Random Data Read Operation                                     |         |

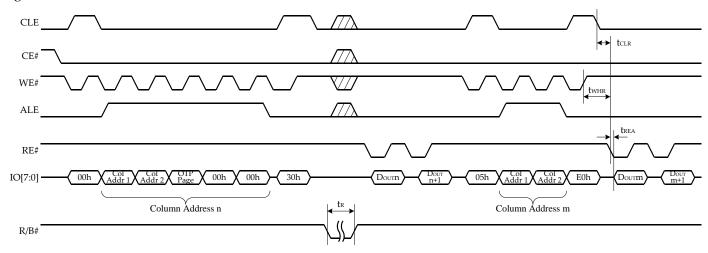

| Figure 69: Two-Plane Page Read                                                               |         |

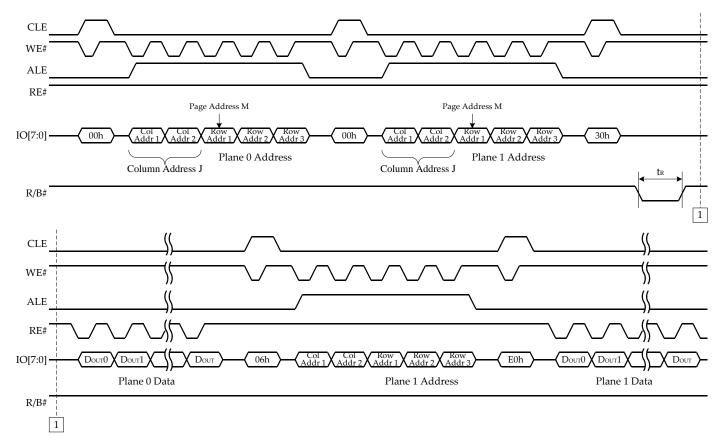

| Figure 70: Two-Plane Page Read with Random Data Read                                         |         |

| Figure 71: Two-Plane Program Page                                                            |         |

| Figure 72: Two-Plane Program Page with Random Data Input                                     |         |

| Figure 73: Two-Plane Program Page Cache Mode                                                 |         |

| Figure 74: Two-Plane Internal Data Move                                                      |         |

| Figure 75: Two-Plane Internal Data Move with Two-Plane Random Data Read                      |         |

| Figure 76: Two-Plane Internal Data Move with Random Data Input                               |         |

| Figure 77: Two-Plane Block Erase                                                             |         |

| Figure 78: Two-Plane / Multiple-Die Read Status Cycle                                        |         |

| Figure 79: Part Numbering Information                                                        |         |

| Figure 80: 48-Pin TSOP – Type 1, CPL (Top View)                                              |         |

| Figure 81: 63-Ball VFBGA, x8 (Balls Down, Top View)                                          |         |

| Figure 82: 63-Ball VFBGA, x6 (Balls Down, Top View)                                          |         |

| Figure 82: 65-Ball VFBGA, x16 (Balls Down, 10p View)<br>Figure 83: 48-Pin TSOP – Type 1, CPL |         |

| Figure 84: 63-Ball VFBGA (10.5mm x 13mm)                                                     |         |

| -                                                                                            |         |

| Figure 85: 63-Ball VFBGA (9mm x 11mm)                                                        | 72      |

**Product Specification**

### **Tables**

| Table 1: Product List                                                | 9  |

|----------------------------------------------------------------------|----|

| Table 2: Pin Definitions                                             | 9  |

| Table 3: Memory Array Addressing                                     |    |

| Table 4: Command Set                                                 |    |

| Table 5: Two-Plane Command Set                                       |    |

| Table 6: Feature Address Definitions                                 |    |

| Table 7: Feature Address 01h: Timing Mode                            |    |

| Table 8: Feature Address 80h: I/O Drive Strength                     |    |

| Table 9: Feature Address 81h: Programmable R/B# Pull-Down Strength   | 15 |

| Table 10: Feature Address 90h – OTP Mode                             | 15 |

| Table 11: Device ID: Manufacturer ID (Address = 00h)                 |    |

| Table 12: Device ID: ONFI Signature (Address = 20h)                  |    |

| Table 13: Parameter Page Definition                                  |    |

| Table 14: Unique ID and Its Complement                               | 19 |

| Table 15: Status Register Definition                                 | 19 |

| Table 16: Block Lock Addressing                                      |    |

| Table 17: Block Lock Status Register Bit Definition                  |    |

| Table 18: Asynchronous Interface Mode Selection                      | 22 |

| Table 19: Error Management Details                                   | 58 |

| Table 20: Spare Area Mapping (x8)                                    | 59 |

| Table 21: Absolute Maximum Ratings                                   | 59 |

| Table 22: Recommended Operating Conditions                           | 60 |

| Table 23: Valid Blocks                                               | 60 |

| Table 24: Capacitance                                                | 60 |

| Table 25: Test Conditions                                            | 60 |

| Table 26: DC Characteristics and Operating Conditions (3.3V)         | 60 |

| Table 27: DC Characteristics and Operating Conditions (1.8V)         | 61 |

| Table 28: AC Characteristics: Command, Data and Address Input (3.3V) | 62 |

| Table 29: AC Characteristics: Command, Data and Address Input (1.8V) | 62 |

| Table 30: AC Characteristics: Normal Operation (3.3V)                | 63 |

| Table 31: AC Characteristics: Normal Operation (1.8V)                |    |

| Table 32: Program/Erase Characteristics                              | 64 |

|                                                                      |    |

#### DS009 (v1.0) Oct 28, 2020

### 1. Features

- Command Set

- ONFI 1.0 Compliant

- X8 I/O Bus

- NAND Interface

- SLC Technology

- Address / Data Multiplexing

- Power Supply Voltage

- Vcc : 2.7V ~ 3.6V

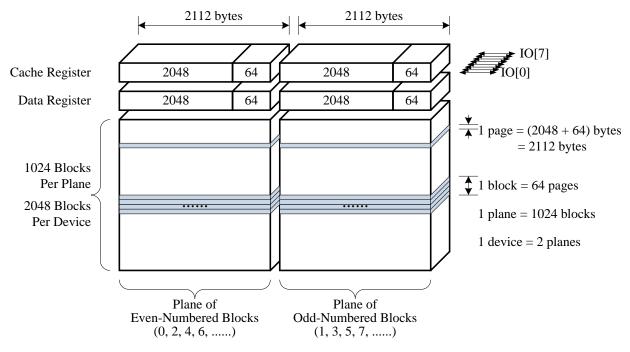

#### • Memory Cell Array Organization (with spare)

- Page size: 2112 bytes (2048 + 64 bytes)

- Block size: 64 pages (128K + 4K bytes)

- Plane size: 2 planes X 1024 blocks per plane

- Device size: 2048 blocks = 2Gbit

- I/O Performance

- Page Read: 25us Max without internal ECC 70us Max with internal ECC

- Page Program: 600us Max (with or without internal ECC)

### Internal Data Move

- Fast data copy without external buffering

- Cache Program

- Improves program throughput with internal buffer

**Product Specification**

- Read Cache

- Improves read throughput

- Fast Block Erase

- Block erase time: 0.7ms Typ, 3ms Max

- Electronic Signature

- ONFI Signature

- Unique ID

- Status Register

- Data Integrity

- Data retention: 10 years

- Endurance: 100K Program / Erase cycles

- Operating Temperature Range

-40°C to 85°C

- Package

- FBGA63

### 2. General Description

The NeuMem NM9A02G08 is a 2Gbit Parallel NAND Flash device with internal ECC that complies with ONFI 1.0 specification. The device includes industry-standard features, which provides cost-effective solution for applications requiring high-density, solid-sate storage. The device is a single-die package. It employs a multiplexed 8-bit bus (IO[7:0]) to convey command, address and data, and the bus interface protocol is controlled by signals: ALE, CE#, CLE, RE# and WE#. Additional signals implementing block lock (LOCK), hardware write protection (WP#) and device status monitor (R/B#) are also available.

The device has a traditional NAND interface that does not include a clock signal. It uses RE# to latch data read, and WE# to latch data written. Commands, Addresses and Data are asynchronously introduced using the control pins.

Program operation is done on a page basis; each page of data can be programmed in tPROG (internal ECC disabled) or tPROG\_ECC (internal ECC enabled). Erase operation is done on each block, and a block is erased in

tBERS. An on-chip controller automates program and erase operations by performing required internal tasks.

Figure 1: Logic Diagram

### 2.1. Product List

Table 1: Product List

| v 35         |                  |      |         |  |  |  |

|--------------|------------------|------|---------|--|--|--|

| Part Number  | Device Interface | Vcc  | Package |  |  |  |

| NM9A02G08AFI | x8 bit           | 3.3V | FBGA63  |  |  |  |

### 2.2. Pin Description

A full description of all pins of the device is offered in the following table.

#### Table 2: Pin Definitions

| Signal | Direction | Description                                                                  |  |

|--------|-----------|------------------------------------------------------------------------------|--|

| ALE    | Input     | Address Latch Enable                                                         |  |

|        |           | When ALE is High, it indicates an address bus cycle.                         |  |

| CE#    | Input     | Chip Enable                                                                  |  |

|        |           | The CE# active-low input selects the device. When CE# is high and the device |  |

|        |           | is in Ready state, the device goes into standby mode.                        |  |

| CLE    | Input     | Command Latch Enable                                                         |  |

|        |           | When CLE is High, it indicates a command bus cycle.                          |  |

| LOCK   | Input     | Block Lock.                                                                  |  |

|        |           | The Block Lock function is enabled if LOCK pin is 1 while the device is powe |  |

|        |           | up. The function is disabled if LOCK is 0 or unconnected during power up.    |  |

|        |           | This pin has internal pull-down resistor.                                    |  |

| RE#    | Input     | Read Enable True                                                             |  |

|        |           | The falling edge of RE# drives internal data to the IO[7:0] bus.             |  |

| WE#     | Input  | Write Enable                                                                   |

|---------|--------|--------------------------------------------------------------------------------|

|         |        | Data, command and address are latched on the rising edge of WE#.               |

| WP#     | Input  | Write Protect                                                                  |

|         |        | The WP# active-low input disables Flash array PROGRAM and ERASE                |

|         |        | operations.                                                                    |

| IO[7:0] | I/O    | Data Inputs/Outputs                                                            |

|         |        | The 8-bit-wide bidirectional I/O bus conveys command, address and data to      |

|         |        | and from the device.                                                           |

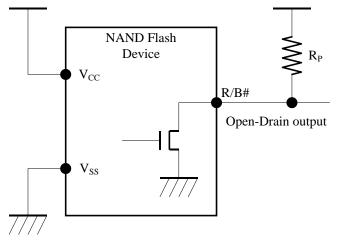

| R/B#    | Output | Ready/Busy                                                                     |

|         |        | The R/B# pin is an open drain output that requires an external pull-up. This   |

|         |        | signal indicates the device status. When R/B# is low, it indicates that one or |

|         |        | more LUN operations are in progress.                                           |

| Vcc     | Supply | Power Supply                                                                   |

|         |        | Power supply for the device.                                                   |

| Vss     | Supply | Ground                                                                         |

|         |        | Power supply ground.                                                           |

|         |        | No Internal Connection                                                         |

|         |        | A NC pin has no internal connection; it can be either unconnected or driven.   |

| DNU     | -      | Do Not Use                                                                     |

|         |        | A DNU pin should be unconnected.                                               |

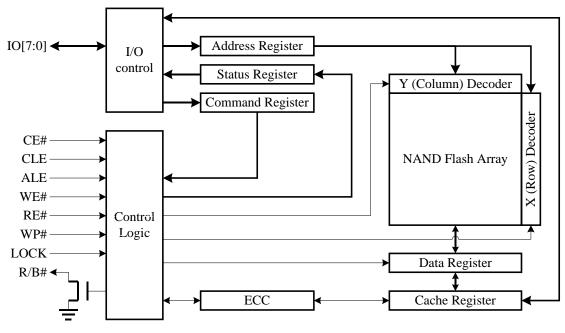

### 2.3. Block Diagram

The device uses NAND Flash cell array to store data. Device operations are implemented through a series of internal registers. A block diagram of the device is shown below.

Figure 2: NAND Flash Block Diagram

### 2.4. Memory Organization

The device memory array is organized in descending hierarchical order: plane, block, page and column. Data is programmed and read in page-based operations, and erase operations shall occur in a block-based manner. The devices are erased upon delivery. Due to device physics limitations, any programmed page address in the

device is not eligible for another program operation and it has to be explicitly erased to make it available for upcoming program operations.

The memory organization is shown in the following figure.

**Figure 3: Array Organization**

### 2.5. Array Addressing

The device memory array addressing is defined as follows.

| Table 3. | Memory  | / Arrav | Addressing |

|----------|---------|---------|------------|

| Table 5: | wernory | y Array | Addressing |

| Bus Cycle             | IO[7]  | IO[6]  | IO[5]  | IO[4]  | IO[3]  | IO[2]  | IO[1] | IO[0]  |  |  |

|-----------------------|--------|--------|--------|--------|--------|--------|-------|--------|--|--|

| 1 <sup>st</sup> Cycle | CA[7]  | CA[6]  | CA[5]  | CA[4]  | CA[3]  | CA[2]  | CA[1] | CA[0]  |  |  |

| 2 <sup>nd</sup> Cycle | Low    | Low    | Low    | Low    | CA[11] | CA[10] | CA[9] | CA[8]  |  |  |

| 3 <sup>rd</sup> Cycle | BA[7]  | BA[6]  | PA[5]  | PA[4]  | PA[3]  | PA[2]  | PA[1] | PA[0]  |  |  |

| 4 <sup>th</sup> Cycle | BA[15] | BA[14] | BA[13] | BA[12] | BA[11] | BA[10] | BA[9] | BA[8]  |  |  |

| 5 <sup>th</sup> Cycle | Low    | Low    | Low    | Low    | Low    | Low    | Low   | BA[16] |  |  |

#### Notes:

- 1. BA = Block Address, PA = Page Address, CA = Column Address.

- 2. Actual page address = BA + PA.

- 3. If CA[11]=1, then CA[10:6] should be all 0s.

- 4. BA[6] is for plane selection.

### 2.6. Command Set

All commands supported by the device are defined in the following table.

| Table 4: Command Set |                              |                   |                         |                              |                                    |                                 |  |  |  |  |

|----------------------|------------------------------|-------------------|-------------------------|------------------------------|------------------------------------|---------------------------------|--|--|--|--|

| Command              | 1 <sup>st</sup> Cmd<br>Cycle | Address<br>Cycles | Data<br>Input<br>Cycles | 2 <sup>nd</sup> Cmd<br>Cycle | Valid When<br>Selected<br>LUN Busy | Valid When<br>Other LUN<br>Busy |  |  |  |  |

| Reset                | FFh                          | 0                 | -                       | -                            | Yes                                | Yes                             |  |  |  |  |

| Read ID              | 90h                          | 1                 | -                       | -                            | No                                 | No                              |  |  |  |  |

| Read Parameter Page  | ECh                          | 1                 | -                       | -                            | No                                 | No                              |  |  |  |  |

## NM9A02G08AFI

| Read Unique ID                 | EDh | 1 | -        | -   | No  | No  |

|--------------------------------|-----|---|----------|-----|-----|-----|

| Get Features                   | EEh | 1 | -        | -   | No  | No  |

| Set Features                   | EFh | 1 | 4        | -   | No  | No  |

| Read Status                    | 70h | 0 | -        | -   | Yes |     |

| Read Status Enhanced           | 78h | 3 | -        | -   | Yes | Yes |

| Random Data Read               | 05h | 2 | -        | E0h | No  | Yes |

| Random Data Input              | 85h | 2 | Optional | -   | No  | Yes |

| Program For Internal Data Move | 85h | 5 | Optional | -   | No  | Yes |

| Read Mode                      | 00h | 0 | -        | -   | No  | Yes |

| Read Page                      | 00h | 5 | -        | 30h | No  | Yes |

| Read Page Cache Sequential     | 31h | 0 | -        | -   | No  | Yes |

| Read Page Cache Random         | 00h | 5 | -        | 31h | No  | Yes |

| Read Page Cache Last           | 3Fh | 0 | -        | -   | No  | Yes |

| Program Page                   | 80h | 5 | Yes      | 10h | No  | Yes |

| Program Page Cache             | 80h | 5 | Yes      | 15h | No  | Yes |

| Erase Block                    | 60h | 3 | -        | D0h | No  | Yes |

| Read For Internal Data Move    | 00h | 5 | -        | 35h | No  | Yes |

| Program For Internal Data Move | 85h | 5 | Optional | 10h | No  | Yes |

| Block Unlock Low               | 23h | 3 | -        | -   | No  | Yes |

| Block Unlock High              | 24h | 3 | -        | -   | No  | Yes |

| Block Lock                     | 2Ah | 1 | -        | -   | No  | Yes |

| Block Lock-Tight               | 2Ch | - | -        | -   | No  | Yes |

| Block Lock Read Status         | 7Ah | 3 | -        | -   | No  | Yes |

| OTP Data Lock By Page (ONFI)   | 80h | 5 | No       | 10h | No  | No  |

| OTP Data Program (ONFI)        | 80h | 5 | Yes      | 10h | No  | No  |

| OTP Data Read (ONFI)           | 00h | 5 | No       | 30h | No  | No  |

#### Notes:

- 1. Busy is denoted by RDY bit in Status Register being 0.

- 2. If a command is valid when other LUNs are busy, it means the command is used in interleaved die operations.

- 3. For Read For internal Data Move and Program For Internal Data Move commands, the operation should stay within plane address boundaries.

- 4. Read Page Cache Sequential, Read Page Cache Random, Read Page Cache Last and Program Page Cache commands are available only when internal ECC is disabled.

- 5. If the previous command is Read Page (00h-30h) or Read Page Cache series command, then a Read Page Cache series command (31h, 00h-31h, 3Fh) while the array is busy (RDY=1, ARDY=0) is supported. Otherwise, it is prohibited.

- 6. If the previous command is Program Page Cache (80h-15h) command, then a Program Page Cavhe (80h-15h) command while the array is busy (RDY=1, ARDY=0) is supported. Otherwise, it is prohibited.

- 7. OTP commands must be placed behind Set Features command with appropriate feature address.

| Command             | 1 <sup>st</sup> Cmd<br>Cycle | Address<br>Cycles | 2 <sup>nd</sup> Cmd<br>Cycle | Address<br>Cycles | 3 <sup>nd</sup> Cmd<br>Cycle | Valid When<br>Selected<br>LUN Busy | Valid When<br>Other LUN<br>Busy |

|---------------------|------------------------------|-------------------|------------------------------|-------------------|------------------------------|------------------------------------|---------------------------------|

| Read Page Two-Plane | 00h                          | 5                 | 00h                          | 5                 | 30h                          | No                                 | Yes                             |

#### Table 5: Two-Plane Command Set

## NM9A02G08AFI

| Read For Two-Plane    | 00h | 5 | 00h     | 5 | 35h | No | Yes |

|-----------------------|-----|---|---------|---|-----|----|-----|

| Internal Data Move    |     |   |         |   |     |    |     |

| Random Data Read      | 06h | 5 | E0h     | - | -   | No | Yes |

| Two-Plane             |     |   |         |   |     |    |     |

| Program Page          | 80h | 5 | 11h-80h | 5 | 10h | No | Yes |

| Two-Plane             |     |   |         |   |     |    |     |

| Program Page Cache    | 80h | 5 | 11h-80h | 5 | 15h | No | Yes |

| Mode Two-Plane        |     |   |         |   |     |    |     |

| Program For Two-Plane | 85h | 5 | 11h-85h | 5 | 10h | No | Yes |

| Internal Data Move    |     |   |         |   |     |    |     |

| Block Erase Two-Plane | 60h | 3 | D1h-60h | - | D0h | No | Yes |

#### Notes:

1. Read For Internal Data Move Two-Plane and Program For Two-Plane Internal Data Move commands should stay within plane boundaries.

- 2. Random Data Read Two-Plane command can only be used with Page Read Two-Plane command.

- 3. For Block Erase Two-Plane command, D1h is not necessary and can be omitted.

- 4. Two-Plane commands are available only when internal ECC is disabled.

### 2.7. OTP Pages

This NAND Flash device contains a one-time-programmable (OTP) area in the LUN, which totally has 30 pages with 2112 bytes in each page. The page address of OTP area ranges from 02h, 03h, 04h through to 1Fh. All OTP pages are guaranteed to be good.

The device is shipped from the factory with all OTP bits being 1. Programming and partial-page programming operations can convert OTP bits from 1 to 0, but once it becomes 0 it can never return to 1. Erase operations have no effect in OTP area, regardless of its protect status. The user may also choose to protect the OTP area to prevent any further programming operations.

OTP operations can be accomplished only when the device is in OTP mode. By setting specific feature bits using Set Features (EFh) commands, the user can enter or exit OTP mode. The user may also acquire OTP status using Get Features (EEh) commands.

### 2.8. Legacy OTP Commands

For compatibility reasons, the device supports OTP Data Program (A0h-10h), OTP Data Protect (A5h-10h) and OTP Data Read (AFh-30h) commands.

### 2.9. Device Feature Table

Devices are shipped with a feature table inside of the memory array, which is available for the host to determine the current settings of the device. The feature table can be read or modified via the Get Feature or Set Feature commands. Feature information is stored into multiple addresses, as is defined in the following table.

| Feature Address | Definition                           |

|-----------------|--------------------------------------|

| 00h             | Reserved                             |

| 01h             | Timing Mode                          |

| 02h - 7Fh       | Reserved                             |

| 80h             | Programmable I/O Drive Strength      |

| 81h             | Programmable R/B# Pull Down Strength |

| 82h - FFh       | Reserved                             |

#### Table 6: Feature Address Definitions

90h

Array Operation Mode

#### 2.9.1. Feature Address 01h: Timing Mode

The definition of Timing Mode feature at address 01h is given below.

#### Table 7: Feature Address 01h: Timing Mode

| Subfeature<br>Parameter | Bit 7          | Bit 6 | Bit 5        | Bit 4   | Bit 3              | Bit 2 | Bit 1 | Bit 0 |  |

|-------------------------|----------------|-------|--------------|---------|--------------------|-------|-------|-------|--|

| P1                      |                |       | Reserved (0) |         | Timing Mode Number |       |       |       |  |

| P2                      |                |       |              | Reserve | ed (00h)           |       |       |       |  |

| Р3                      |                |       |              | Reserve | ed (00h)           |       |       |       |  |

| P4                      | Reserved (00h) |       |              |         |                    |       |       |       |  |

#### Notes:

- 1. Reserved: Reserved values are zero by default.

- 2. This feature address determines the maximum speed of the device.

- 3. The device is in the default Mode 0 upon power-up.

- 4. Timing Mode Number:

- Mode 0 = 000 (default)

- Mode 1 = 001

- Mode 2 = 010

- Mode 3 = 011

- Mode 4 = 100

- Mode 5 = 101

- 5. Modes 0 through 4 apply to 1.8V and 3.3V operations.

- 6. Mode 5 only applies to 3.3V operations.

#### 2.9.2. Feature Address 80h: Programmable I/O Drive Strength

The device I/O drive strength setting can be selected at Feature Address 80h.

#### Table 8: Feature Address 80h: I/O Drive Strength

| Subfeature<br>Parameter | Bit 7          | Bit 6                           | Bit 5 | Bit 4   | Bit 3    | Bit 2 | Bit 1 | Bit 0 |  |  |  |  |

|-------------------------|----------------|---------------------------------|-------|---------|----------|-------|-------|-------|--|--|--|--|

| P1                      |                | Reserved (0) I/O Drive Strength |       |         |          |       |       |       |  |  |  |  |

| P2                      |                |                                 |       | Reserve | ed (00h) |       |       |       |  |  |  |  |

| Р3                      |                |                                 |       | Reserve | ed (00h) |       |       |       |  |  |  |  |

| P4                      | Reserved (00h) |                                 |       |         |          |       |       |       |  |  |  |  |

Notes:

- 1. Reserved: Reserved values are zero by default.

- 2. This feature address determines the device I/O drive strength, which should be selected based on the bus loading.

- 3. The device is in full strength upon power-up.

- 4. I/O Drive Strength:

| Full           | = 00b (default) |

|----------------|-----------------|

| Three-quarters | = 01b           |

| One-half       | = 10b           |

| One-quarter    | = 11b           |

### 2.9.3. Feature Address 81h: Programmable R/B# Pull-Down Strength

The pull-down strength at R/B# pin of the device can be selected at Feature Address 81h.

#### Table 9: Feature Address 81h: Programmable R/B# Pull-Down Strength

|                         |       |       |                            | 5        |  |  |  |

|-------------------------|-------|-------|----------------------------|----------|--|--|--|

| Subfeature<br>Parameter | Bit 7 | Bit 6 | Bit 1                      | Bit 0    |  |  |  |

| P1                      |       |       | R/B# Pull-Down<br>Strength |          |  |  |  |

| P2                      |       |       | Reserve                    | ed (00h) |  |  |  |

| Р3                      |       |       | Reserve                    | ed (00h) |  |  |  |

| P4                      |       |       | Reserve                    | ed (00h) |  |  |  |

#### Notes:

- 1. Reserved: Reserved values are zero by default.

- 2. This feature address determines the R/B# pull-down strength, which should be selected based on the loading of R/B# pin.

- 3. The device is in full strength upon power-up.

- 4. R/B# Pull-Down Strength:

Full= 00b (default)Three-quarters= 01bOne-half= 10bOne-quarter= 11b

#### 2.9.4. Feature Address 90h: Array Operation Mode

Feature address 90h determines the operation mode of the device.

#### Table 10: Feature Address 90h – OTP Mode

| Subfeature<br>Parameter | Bit 7 | Bit 6          | Bit 2   | Bit 1   | Bit 0          |  |  |  |  |  |  |

|-------------------------|-------|----------------|---------|---------|----------------|--|--|--|--|--|--|

| P1                      |       | Reserv         | ved (0) |         | Operation Mode |  |  |  |  |  |  |

| P2                      |       |                |         | Reserve | ed (00h)       |  |  |  |  |  |  |

| P3                      |       | Reserved (00h) |         |         |                |  |  |  |  |  |  |

| P4                      |       | Reserved (00h) |         |         |                |  |  |  |  |  |  |

#### Notes:

- 1. Reserved: Reserved values are zero by default.

- 2. The operation mode bits are reset to 0s upon power-up.

- 3. Operation Mode in terms of OTP operation:

- Normal= 0000bOTP operation= 0001bOTP protection= 0011b

- 4. Operation Mode in terms of internal ECC:

- Disable ECC = 0000b

- Enable ECC = 1000b

#### 2.10. Device ID

The NAND Flash devices are shipped with identification codes to provide information on device type, manufacturer ID, device configurations, etc.

### 2.10.1. ID: Address 00h

Device ID at address 00h provides device specific information including manufacturer code, device identifier, flash array cell type, page size, among many other device configurations.

Table 11: Device ID: Manufacturer ID (Address = 00h)

|        | Table 11: Device ID: Manufacturer ID (Address = 00n) |                   |     |     |     |     |     |     |     |     |        |  |

|--------|------------------------------------------------------|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|--------|--|

| #      | Parameter                                            | Options           | IO7 | IO6 | IO5 | IO4 | IO3 | IO2 | IO1 | IO0 | Value  |  |

| Byte 0 | JEDEC Manufacturer ID                                | NeuMem            | 0   | 0   | 1   | 0   | 1   | 1   | 0   | 0   | 2Ch    |  |

| Byte 1 | Device ID                                            | NM9A02G08AFI      | 1   | 1   | 0   | 1   | 1   | 0   | 1   | 0   | DAh    |  |

| Byte 2 | Number of die per CE                                 | 1                 |     |     |     |     |     |     | 0   | 0   | 00b    |  |

|        | Cell type                                            | SLC               |     |     |     |     | 0   | 0   |     |     | 00b    |  |

|        | Number of                                            | 2                 |     |     | 0   | 1   |     |     |     |     | 01b    |  |

|        | simultaneously                                       |                   |     |     |     |     |     |     |     |     |        |  |

|        | programmed pages                                     |                   |     |     |     |     |     |     |     |     |        |  |

|        | Interleaved operations                               | Not Supported     |     | 0   |     |     |     |     |     |     | 0b     |  |

|        | between multiple die                                 |                   |     |     |     |     |     |     |     |     |        |  |

|        | Cache programming                                    | Supported         | 1   |     |     |     |     |     |     |     | 1b     |  |

|        | Byte Value                                           | NM9A02G08AFI      | 1   | 0   | 0   | 1   | 0   | 0   | 0   | 0   | 90h    |  |

| Byte 3 | Page size                                            | 2KB               |     |     |     |     |     |     | 0   | 1   | 01b    |  |

|        | Spare area size (bytes)                              | 64B               |     |     |     |     |     | 1   |     |     | 1b     |  |

|        | Block size (without                                  | 128KB             |     |     | 0   | 1   |     |     |     |     | 01b    |  |

|        | spare)                                               |                   |     |     |     |     |     |     |     |     |        |  |

|        | Organization                                         | x8                |     | 0   |     |     |     |     |     |     | 0b     |  |

|        |                                                      | x16               |     | 1   |     |     |     |     |     |     | 1b     |  |

|        | Serial access (MIN)                                  | 1.8V: 25ns        | 0   |     |     |     | 0   |     |     |     | 0xxx0b |  |

|        |                                                      | 3.3V: 20ns        | 1   |     |     |     | 0   |     |     |     | 1xxx0b |  |

|        | Byte Value                                           | NM9A02G08AFI      | 1   | 0   | 0   | 1   | 0   | 1   | 0   | 1   | 95h    |  |

| Byte 4 | ECC level                                            | 4-bit ECC / 512   |     |     |     |     |     |     | 1   | 0   | 10b    |  |

|        |                                                      | (main)            |     |     |     |     |     |     |     |     |        |  |

|        |                                                      | + 4 (spare)       |     |     |     |     |     |     |     |     |        |  |

|        |                                                      | +8 (parity) bytes |     |     |     |     |     |     |     |     |        |  |

|        | Planes per CE#                                       | 2                 |     |     |     |     | 0   | 1   |     |     | 01b    |  |

|        | Plane size                                           | 1Gb               |     | 0   | 0   | 0   |     |     |     |     | 000b   |  |

|        | Internal ECC                                         | ECC disabled      | 0   |     |     |     |     |     |     |     | 0b     |  |

|        | -                                                    | ECC enabled       | 1   |     |     |     |     |     |     |     | 1b     |  |

|        | Byte Value                                           | NM9A02G08AFI      | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 0   | 06h    |  |

### 2.10.2. ID: Address 20h (ONFI Signature)

Command 90h in combination with an address of 20h retrieves ONFI signature from the device, indicating that the device supports ONFI specification.

The ONFI signature is the ASCII encoding of "ONFI" where 'O' = 4Fh, 'N' = 4Eh, 'F' = 46h, and 'I' = 49h.

Table 12: Device ID: ONFI Signature (Address = 20h)

| #      | Description | IO7 | IO6 | IO5 | IO4 | IO3 | IO2 | IO1 | IO0 | Value |

|--------|-------------|-----|-----|-----|-----|-----|-----|-----|-----|-------|

| Byte 0 | "O"         | 0   | 1   | 0   | 0   | 1   | 1   | 1   | 1   | 4Fh   |

| Byte 1 | "N"         | 0   | 1   | 0   | 0   | 1   | 1   | 1   | 0   | 4Eh   |

| Byte 2 | "F"         | 0   | 1   | 0   | 0   | 0   | 1   | 1   | 0   | 46h   |

## NM9A02G08AFI

| #      | Description | IO7 | IO6 | IO5 | IO4 | IO3 | IO2 | IO1 | IO0 | Value |

|--------|-------------|-----|-----|-----|-----|-----|-----|-----|-----|-------|

| Byte 3 | "I"         | 0   | 1   | 0   | 0   | 1   | 0   | 0   | 1   | 49h   |

| Byte 4 | Undefined   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | XXh   |

### 2.11. Parameter Page

Parameter page is a data structure that describes the device's organization, features, timings and other behavioral parameters, offering a means to provide the host with sufficient information necessary to successfully communicate with the NAND Flash device.

The following table defines the parameter page data structure. To ensure the reliability of parameter data storage, x8 devices contain at least eight copies of the parameter page, and x16 devices contain at least four copies. If CRC checking indicates an incorrect copy is retrieved by the initial Read Parameter Page (ECh) command, the command can be resent to the device until a valid copy is available.

| Byte    | Description                   |              | Value                                   |  |  |

|---------|-------------------------------|--------------|-----------------------------------------|--|--|

| 0-3     | Parameter page signature:     |              | 4Fh, 4Eh, 46h, 49h                      |  |  |

|         | 4Fh is ASCII for "O";         |              |                                         |  |  |

|         | 4Eh is ASCII for "N";         |              |                                         |  |  |

|         | 46h is ASCII for "F";         |              |                                         |  |  |

|         | 49h is ASCII for "I".         |              |                                         |  |  |

| 4-5     | Revision number               | 1            | 02h, 00h                                |  |  |

| 6-7     | Features supported            | NM9A02G08AFI | 18h, 00h                                |  |  |

| 8-9     | Optional commands supporte    | d            | 3Fh, 00h                                |  |  |

| 10-31   | Reserved.                     |              | 00h, 00h, 00h, 00h, 00h, 00h, 00h, 00h, |  |  |

|         |                               |              | 00h, 00h, 00h, 00h, 00h, 00h, 00h, 00h, |  |  |

|         |                               |              | 00h, 00h, 00h, 00h, 00h, 00h            |  |  |

| 32-43   | Device manufacturer           |              | 4Dh, 49h, 43h, 52h, 4Fh, 4Eh, 20h, 20h, |  |  |

|         |                               |              | 20h, 20h, 20h, 20h                      |  |  |

| 44-63   | Device model                  | NM9A02G08AFI | 4Dh, 54h, 32h, 39h, 46h, 32h, 47h, 30h, |  |  |

|         |                               |              | 38h, 41h, 42h, 41h, 45h, 41h, 48h, 34h, |  |  |

|         |                               |              | 20h, 20h, 20h, 20h                      |  |  |

| 64      | Manufacturer ID               |              | 2Ch                                     |  |  |

| 65-66   | Date code.                    |              | 00h, 00h                                |  |  |

| 67-79   | Reserved.                     |              | 00h, 00h, 00h, 00h, 00h, 00h, 00h, 00h, |  |  |

|         |                               |              | 00h, 00h, 00h, 00h, 00h                 |  |  |

| 80-83   | Number of data bytes per pag  | e.           | 00h, 08h, 00h, 00h                      |  |  |

| 84-85   | Number of spare bytes per pa  | ge.          | 40h, 00h                                |  |  |

| 86-89   | Number of data bytes per part | tial page.   | 00h, 02h, 00h, 00h                      |  |  |

| 90-91   | Number of spare bytes per pa  | rtial page.  | 10h, 00h                                |  |  |

| 92-95   | Number of pages per block.    |              | 40h, 00h, 00h, 00h                      |  |  |

| 96-99   | Number of blocks per logical  | unit.        | 00h, 08h, 00h, 00h                      |  |  |

| 100     | Number of logical units.      |              | 01h                                     |  |  |

| 101     | Number of address cycles.     |              | 23h                                     |  |  |

| 102     | Number of bits per cell.      |              | 01h                                     |  |  |

| 103-104 | Bad blocks maximum per unit   | t.           | 28h, 00h                                |  |  |

| 105-106 | Block endurance.              |              | 01h, 05h                                |  |  |

#### **Table 13: Parameter Page Definition**

## NM9A02G08AFI

| Byte    | Description                            |                   | Value                                   |

|---------|----------------------------------------|-------------------|-----------------------------------------|

| 107     | Guaranteed valid blocks at beg         | inning of target. | 01h                                     |

| 108-109 | Block endurance for guarantee          | d valid blocks.   | 00h, 00h                                |

| 110     | Number of programs per page            |                   | 04h                                     |

| 111     | Partial programming attributes         | 5.                | 00h                                     |

| 112     | Number of bits ECC correctabi          | lity.             | 04h                                     |

| 113     | Number of interleaved address          | s bits.           | 01h                                     |

| 114     | Interleaved operation attribute        | S.                | 0Eh                                     |

| 115-127 | Reserved.                              |                   | 00h, 00h, 00h, 00h, 00h, 00h, 00h, 00h, |

|         |                                        |                   | 00h, 00h, 00h, 00h, 00h                 |

| 128     | I/O pin capacitance.                   |                   | 0Ah                                     |

| 129-130 | Timing mode support NM9A02G08AFI       |                   | 3Fh, 00h                                |

| 131-132 | Program cache timing mode NM9A02G08AFI |                   | 3Fh, 00h                                |

|         | support.                               |                   |                                         |

| 133-134 | tPROG Maximum page progra              | m time.           | 58h, 02h                                |

| 135-136 | tBERS Maximum block erase ti           | me.               | B8h, 0Bh                                |

| 137-138 | tR Maximum page read time.             |                   | 19h, 00h                                |

| 139-140 | tCCS Minimum.                          |                   | 64h, 00h                                |

| 141-163 | Reserved                               |                   | 00h, 00h, 00h, 00h, 00h, 00h, 00h, 00h, |

|         |                                        |                   | 00h, 00h, 00h, 00h, 00h, 00h, 00h, 00h, |

|         |                                        |                   | 00h, 00h, 00h, 00h, 00h, 00h, 00h       |

| 164-165 | Vendor-specific revision numb          | er.               | 01h, 00h                                |

| 166-253 | Vendor-specific.                       |                   | 01h, 00h, 00h, 02h, 04h, 80h, 01h, 81h, |

|         |                                        |                   | 04h, 01h, 02h, 01h,0Ah, 00h, 00h, 00h,  |

|         |                                        |                   | 00h, 00h, 00h, 00h, 00h, 00h, 00h, 00h, |

|         |                                        |                   | 00h, 00h, 00h, 00h, 00h, 00h, 00h, 00h, |

|         |                                        |                   | 00h, 00h, 00h, 00h,00h, 00h, 00h, 00h,  |

|         |                                        |                   | 00h, 00h, 00h, 00h, 00h, 00h, 00h, 00h, |

|         |                                        |                   | 00h, 00h, 00h, 00h, 00h, 00h, 00h, 00h, |

|         |                                        |                   | 00h, 00h, 00h, 00h, 00h, 00h, 00h, 00h, |

|         |                                        |                   | 00h, 00h, 00h, 00h, 00h, 00h, 00h, 00h, |

|         |                                        |                   | 00h, 00h, 00h, 00h, 00h, 00h, 00h, 00h, |

|         |                                        |                   | 00h, 00h, 00h, 00h,00h, 00h, 00h, 00h(  |

| 254-255 | Integrity CRC.                         |                   | Set during test.                        |

| 256–511 | Value of bytes 0–255.                  |                   |                                         |

| 512–767 | Value of bytes 0–255.                  |                   |                                         |

| 768+    | Additional redundant paramet           | er pages.         |                                         |

### 2.12. Unique ID

The device comes with a Unique ID feature to allow for the implementation of serial number mechanisms which the user may leverage for security considerations. A combination of Unique ID and device manufacturer is truly unique.

The device has sixteen copies of unique ID in its internal memory array, each copy being 32 bytes in length. Within each copy, the first 16 bytes are the unique data, with the second 16 bytes being its complement, which enables the host designer to utilize XOR operation to check data integrity. Should the XOR data check fail, the

host can repeat the XOR operations on subsequent copies until a correct copy is detected.

#### Table 14: Unique ID and Its Complement

| Bytes | Value                           |

|-------|---------------------------------|

| 0-15  | Unique ID                       |

| 16-31 | Unique ID's bit-wise complement |

### 2.13. Status Register

The Status Register offers a means for the host to poll the status of the previous operation. The host can launch either Read Status or Read Status Enhanced operations to retrieve Status Register value from the device. The status register is defined as below.

| SR  | Program | Program Page  | Page Read     | Page Read     | Block Erase   | Description                 |

|-----|---------|---------------|---------------|---------------|---------------|-----------------------------|

| Bit | Page    | Cache Mode    |               | Cache Mode    |               |                             |

| 7   | Write   | Write Protect | Write Protect | Write Protect | Write Protect | 0 = Protected               |

|     | Protect |               |               |               |               | 1 = Not protected           |

| 6   | RDY     | RDY cache     | RDY           | RDY cache     | RDY           | 0 = Busy                    |

|     |         |               |               |               |               | 1 = Ready                   |

| 5   | ARDY    | ARDY          | ARDY          | ARDY          | ARDY          | Don't Care                  |

| 4   | -       | -             | -             | -             | -             | Don't Care                  |

| 3   | -       | -             | Rewrite       | -             | -             | 0 = Normal or uncorrectable |

|     |         |               | recommended   |               |               | 1 = Rewrite recommended     |

| 2   | -       | -             | -             | -             | -             | Don't Care                  |

| 1   | FAILC   | FAILC (N-1)   | Reserved      | -             | -             | Don't Care                  |

|     | (N-1)   |               |               |               |               |                             |

| 0   | FAIL    | FAIL (N)      | FAIL          | -             | FAIL          | 0 = Successful PROGRAM /    |

|     |         |               |               |               |               | ERASE / READ                |

|     |         |               |               |               |               | 1 = Error in PROGRAM /      |

|     |         |               |               |               |               | ERASE / READ                |

#### Table 15: Status Register Definition

#### Notes:

- 1. For simplicity, the acronym "SR" is used throughout the document to denote Status Register.

- 2. SR[6] is 1 when the cache is ready to accept new data.

- 3. R/B# follows the value of SR[6].

- 4. SR[5] is 0 during program operation. In cache mode, this bit is 1 when all internal operations are complete.

- 5. SR[0] being FAIL signifies that an uncorrectable error has occurred.

- 6. SR[6] and SR[5] are shared by all planes on the die (LUN) selected by Read Status Enhanced 78h command.

- 7. SR[1] and SR[0] are specific to the plane specified by the row address, which comes with the Read Status Enhanced 78h command.

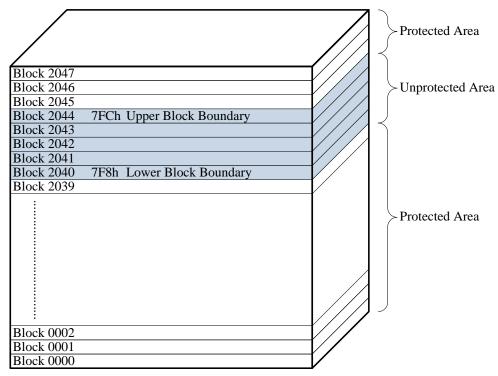

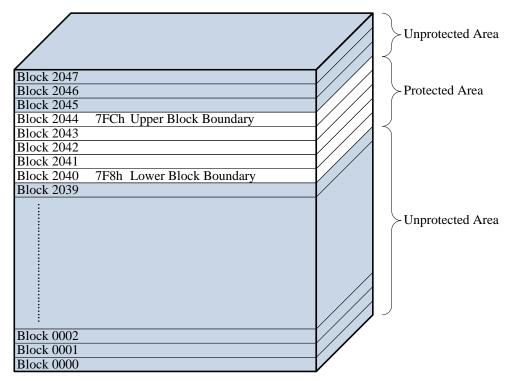

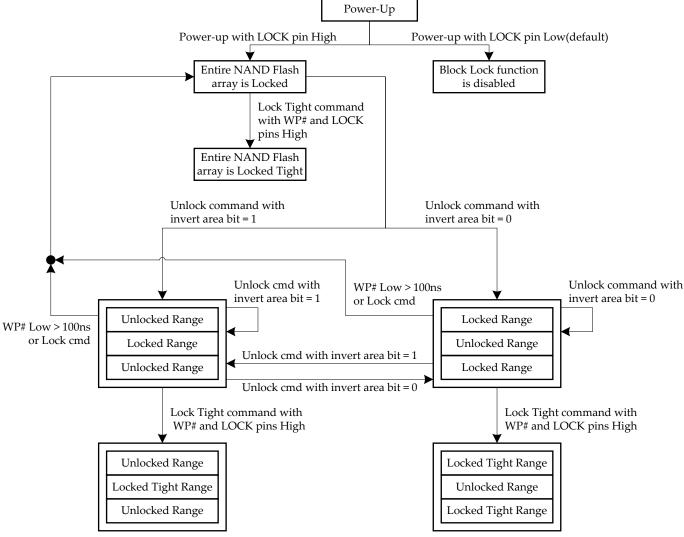

### 2.14. Block Lock Feature

The device has block lock feature which protects a specified range of blocks against program and erase operations. It is preferable to using WP# pin for memory protection.

This feature is determined by the status of LOCK pin at power-up. LOCK being Low at power-up will disable all Block Lock commands. LOCK being High at power-up will enable Block Lock commands, and all blocks are protected by default, regardless of the value of WP# pin. Locked blocks can be locked tight, which disables any locking or unlocking operations on the devices blocks.

In order to modify the content of the memory array of the NAND Flash, unlock operation should be performed.

Program and erase operations take effect only in unlocked address space.

#### 2.14.1. WP# and Block Lock

The rules of WP# and Block Lock mechanism is listed as follows.

- 1. If the blocks are not locked tight, then holding WP# Low locks all blocks.

- 2. If WP# goes Low and High again, then a new Unlock command is needed to unlock blocks if program or erase operations are desired.

### 2.14.2. Boundary Block Address Registers And Invert Area Bit

The range of unlocked blocks is defined by two registers and one control bit:

- 1. Upper boundary block address register;

- 2. Lower boundary block address register (must be less than the upper boundary block address register);

- 3. Invert area bit.

If invert area bit is 0, then the address range between the two registers are unlocked. Otherwise if invert area bit is 1, then the address range outside the two registers are unlocked. See the figures below for demonstration for this mechanism.

Figure 4: Flash Array Protected: Invert Area Bit = 0

## NM9A02G08AFI

Figure 5: Flash Array Protected: Invert Area Bit = 1

### 2.14.3. Block Lock Addressing

The address cycles that accesses the boundary block address registers are defined in the following table. Address cycles following Unlock 23h and 24h commands indicate the lower and upper boundary block address registers, respectively. The LSB of page address corresponds to the invert area bit.

The device allows only one range to be specified by the boundary block address registers. After 23h and 24h unlock commands has taken effect, if more 23h or 24h commands are issued, then these registers will be updated with new values.

| Bus Cycle             | IO[7]  | IO[6]  | IO[5]  | IO[4]  | IO[3]  | IO[2]  | IO[1]  | IO[0]    |

|-----------------------|--------|--------|--------|--------|--------|--------|--------|----------|

| 1 <sup>st</sup> Cycle | BA[7]  | BA[6]  | Low    | Low    | Low    | Low    | Low    | Invert   |

|                       |        |        |        |        |        |        |        | Area Bit |

| 2 <sup>nd</sup> Cycle | BA[15] | BA[14] | BA[13] | BA[12] | BA[11] | BA[10] | BA[9]  | BA[8]    |

| 3 <sup>rd</sup> Cycle | Low    | Low    | Low    | Low    | Low    | Low    | BA[17] | BA[16]   |

Table 16: Block Lock Addressing

#### Notes:

1. The Invert Area Bit is valid in 24h command. It may be Low or High in 23h command.

### 2.14.4. Block Lock Status Register

Block lock status register contains detailed information of the lock or unlock status of a block. The host can poll this register to learn the protection status of a specific block.

| Block Lock Status Register Definition             | IO[7:3] | IO[2] (Lock#) | IO[1] (LT#) | IO[0] (LT) |  |  |  |

|---------------------------------------------------|---------|---------------|-------------|------------|--|--|--|

| Block is locked tight                             | Х       | 0             | 0           | 1          |  |  |  |

| Block is locked                                   | Х       | 0             | 1           | 0          |  |  |  |

| Block is unlocked, and device is locked tight     | Х       | 1             | 0           | 1          |  |  |  |

| Block is unlocked, and device is not locked tight | Х       | 1             | 1           | 0          |  |  |  |

| Notes:                                            |         |               |             |            |  |  |  |

#### Table 17: Block Lock Status Register Bit Definition

1. LT is acronym for Lock Tight.

### 2.14.5. Block Lock Flow

The control flow of block lock mechanism is summarized in the following figure.

Figure 6: Block Lock Flowchart

### 3. Bus Operations

### 3.1. Asynchronous Interface Mode Selection

The mode selection of the bus interface is summarized in the following table.

| Table To. Asynchronous interface mode Selection |     |     |     |     |     |     |        |  |

|-------------------------------------------------|-----|-----|-----|-----|-----|-----|--------|--|

| Mode                                            | CE# | CLE | ALE | WE# | RE# | IOx | WP#    |  |

| Standby                                         | Н   | Х   | Х   | Х   | Х   | Х   | 0V/Vcc |  |

| Command Input                                   | L   | Н   | L   | ٦f  | Н   | Х   | Н      |  |

| Address Input                                   | L   | L   | Н   | ٦f  | Н   | Х   | Н      |  |

| Data Input                                      | L   | L   | L   | ٦f  | Н   | Х   | Н      |  |

| Data Output                                     | L   | L   | L   | Н   | ₽   | Х   | Х      |  |

| Write Protect                                   | Х   | Х   | Х   | Х   | Х   | Х   | L      |  |

Table 18: Asynchronous Interface Mode Selection

#### Notes:

1. H = Logic level HIGH; L = Logic level LOW; X = Logic level HIGH or LOW.

2. WP# should be biased to CMOS Low or High for standby.

The mode selection table is graphically interpreted in the following figures in order to aid understanding. Detailed timing diagrams for the various bus modes will be presented in later section.

### 3.2. Standby

It is a typical practice to drive CE# pin to HIGH when the device is not performing an operation, which puts the devices in standby mode. In standby mode the device is deselected, outputs are disabled, and the device operates at reduced power consumption.

The device has CE# "Don't Care" capability that allows the NAND Flash to share the asynchronous bus with other memory devices: While the current NAND Flash is busy in its internal operations, other devices on the same bus can be accessed. This feature enables the designer to place multiple NAND Flash devices on one asynchronous bus.

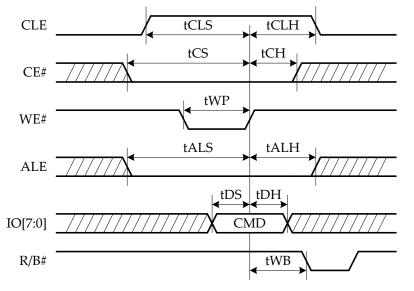

### 3.3. Asynchronous Command Input

Asynchronous command input cycle issues a command to the device, instructing it to perform a certain action. Commands are loaded from IO[7:0] to internal command register by WE# rising edge when CE# is low, CLE is high, ALE is low and RE# is high.

While the device is busy (RDY=0), only Read Status and Read Status Enhanced commands are accepted, while other commands are typically ignored. For commands that modifies (write or erase) any contents in the memory, WP# pin must be high.

Figure 7: Asynchronous Command Input Cycle Timing Diagram

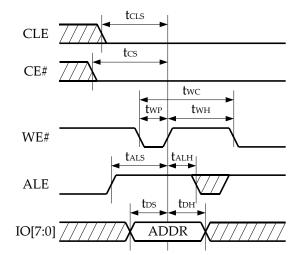

### 3.4. Asynchronous Address Input

Asynchronous address input cycle allows the host to feed the address of a read, program or erase operation to the device. Addresses are loaded from IO[7:0] to internal address register on the rising edge of WE# when CE# is low, ALE is high, CLE is low and RE# is high.

Bits that do not belong to valid address space must be set to low. The number of address cycles is dependent on the command it belongs to; refer to command descriptions for detailed requirements of address cycles.

While the device is busy (RDY=0), only the address of Read Status Enhanced command is accepted, while the address cycles of other commands are typically ignored.

Figure 8: Asynchronous Address Input Cycle Timing Diagram

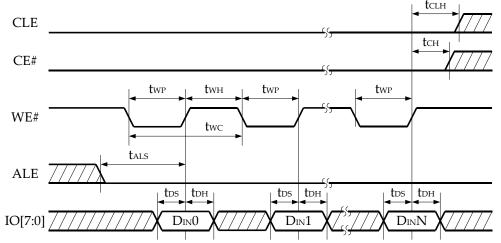

### 3.5. Asynchronous Data Input